## TRANSCEIVERS AND INTERCONNECTS

### **EXECUTIVE SUMMARY**

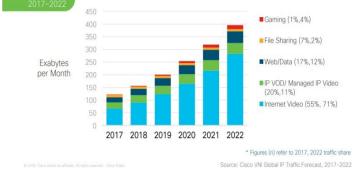

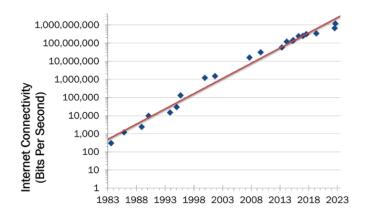

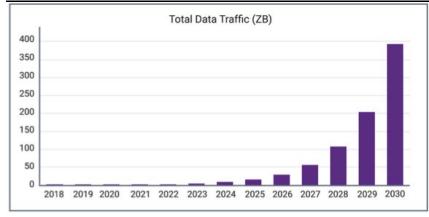

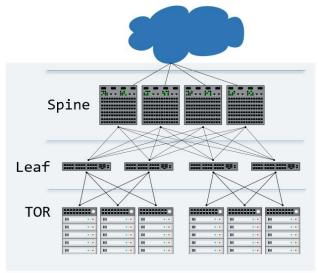

The data explosion generated by the increasing use of social networks, digital entertainment, cloud-computing, and the internet of things (IoT) is radically driving the growth of data centers and the need for high bandwidth, lowlatency, low power consumption, optical fiber-based communications. Since 2022, this growth has accelerated to unprecedented levels due to the rapid adoption of artificial intelligence (AI) in general and generative AI in particular. The dynamics of the market have changed. The datacenter (DC) industry, represented by companies such as Google, Facebook, Microsoft, Amazon etc., not telecommunication companies are driving next-generation technology platforms and metrics. These forces are transforming data center architectures to a higher level of integration of photonics components with fiber interconnects that are becoming more intelligent and higher performing.

The biggest change over the past 3 years in optical interconnects is the commercial introduction of co-package compatible Ethernet switch ASICs and associated optical engines (i.e., transceiver photonic integrated circuits (PICs) without their mechanical envelops). This significant event will spur a move to innovative, lower cost detachable connectors from legacy technology - fiber array in glass V-grooves, known as fiber array units or FAUs) that are actively aligned by optical power-peaking and then bonded to the PIC with UV/thermally cured epoxy. Total cost of ownership dominates the decision process for technology adoption and fiber attach is one of the highest categories of the cost pareto. In addition, FAUs, as a 30-year-old technology, is well down its cost reduction curve. The expected interconnect cost reduction from new, lower-cost, co-packaged PIC-to-fiber solutions should motivate front panel, pluggable transceivers are not going away and have a path to 1.6 Tbps and perhaps 3.2 Tbps. The recently announced OSFP-XD multi-source agreement (MSA) follows the historic path of increased parallelism (more channels) but existing and limited faceplate area will drive innovations in small form factor connectors. Likewise co-packaged connectors (both PIC and front panel) will need to be small, and cross-fertilization of space-constrained solutions are anticipated. Another important trend will be automation, which will be critical to achieve the rate of manufacturing predicted by transceiver sales volume. And new technologies such as glass waveguides and expanded beam optics will provide next generation photonic solutions leading transparency of outsourced assembly & test (OSAT) that finally fulfills the promise of silicon integrated photonics, not only tapping into the scale possible with semiconductor wafer-scale fabrication and the leveraging of the silicon integrated circuit ecosystem, but with back-end high speed assembly and packaging. "At this point, high-volume manufacturing abilities are critical to meet the demand for data center optics." [1]

### INTRODUCTION

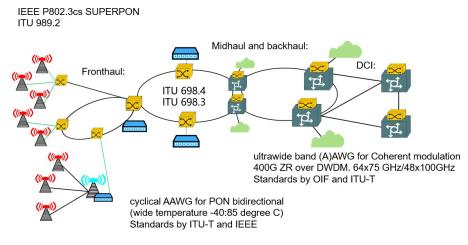

Three major segments exist in the datacom and telecom market: Telecom core/metro, telecom access, and datacom. While this report will continue to use the phrase "datacom", it is important to point out interchangeably using the phrase "datacenter" would be acceptable given the dominance of this sub-sector in driving revenue and innovation in this segment. The growth of the telecom core/metro and datacom segments are expected to experience very strong growth over the next decade. Within that growth is the trend to photonics components integrated in PICs which is beginning to accelerate driven by applications that require smaller photonic component solutions, lower power consumption, higher data rates, hybrid packaging, longer interconnect lengths, and scaled economics in terms of \$/Gbps. In particular, PIC transceivers are expected to grow quickly over the next decade from the rapid ramping in deployment of 800Gbps systems using 60 to 80GHz bandwidth photonic devices. Within 5 years, 1600Gbps and 3200Gbps are expected.

### **IPSR-I DATACENTERS & TELECOM**

The obvious yet most difficult next move is to increase the optoelectronic modulation and detection speed from 60-80 GHz to beyond 100 GHz. Recall that 40 GHz analogue bandwidth roughly corresponds to approximately 50 Gbaud NRZ using standing coding techniques and 100Gbps PAM4<sup>1</sup> while 70 GHz analogue bandwidth corresponds to ~100 Gbaud NRZ, and 200Gbps PAM4. Subsequently, 100GHz analogue bandwidth corresponds to ~150 Gbaud NRZ, and 300Gbps PAM4. At the same time, these new optoelectronic devices must be very small, and operate with very low voltage to keep power consumption low.

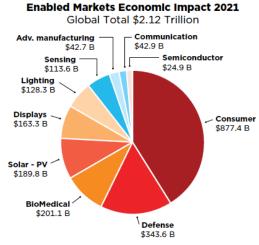

Optical interconnects focus on optical connections between photonic integrated circuits (PICs) in either computer servers or Ethernet ASIC switches and other equipment used in cloud and hyperscale data centers and other high-performance data communications applications such as AI and machine learning (ML). This market has significant strategic importance due to the transition from discrete server systems used in millions of businesses and institutions (enterprise DCs) to large, independent, Cloud Data-As-A-Service (DAAS) providers. Hyperscale data centers (HDCs) are becoming THE key elements of our future information technology infrastructure. The emphasis is on DCs since this application was the first and remains the dominant one for PIC optical interconnects.

For applications outside communications, interconnect systems requirements are generally similar to communications applications, that is, determined by the distance of optical propagation involved. However, there are areas where the different types of application requirements diverge, such as:

- Medical/bioweapons sensing and radar requiring high robustness which may not be subject to the same cost constraints as typical communication applications

- Many sensing applications which require the integration of microfluidic elements, may require wavelengths of operation outside the standard tele/datacom 1.3/1.5 μm bands, and have potentially lower cost and more relaxed loss targets

- Quantum applications where loss targets are significantly lower than DC

- Neuromorphic computing based on integrated photonic accelerators requiring high speed and highly parallel interconnects between the accelerator and CPU/memory to overcome the electronic memory and pin constraints; photonic links could provide the necessary scale. [2]

In the DC application space, silicon PIC (SiP) transceivers have taken over the 100-to-500-meter space due to their cost competitiveness and ability to meet link requirements. Much of the focus is on SiP but also applies to other material systems (i.e., indium phosphide, InP, and gallium arsenide, GaAs). In fact, the manufacturing scale section parses the three material systems.

### PURPLE BRICK WALL FOR TRANSCEIVERS

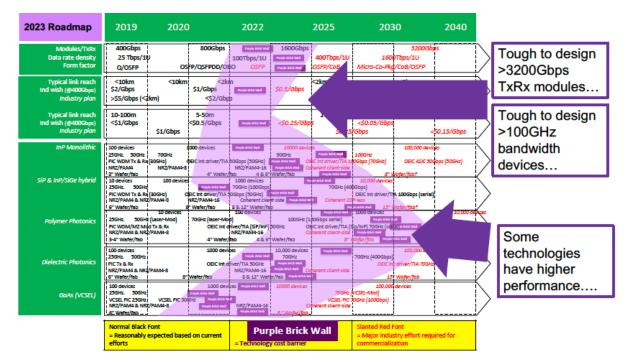

The transceiver/modules roadmap that displays the purple brick walls is shown below in Figure 1 and Figure 2. Figure 1 shows the individual purple brick walls for each technology segment. Figure 2 shows the purple brick wall challenges that require focus to achieve the metrics laid out in the transceiver/module roadmap.

<sup>&</sup>lt;sup>1</sup> <u>https://www.edn.com/the-fundamentals</u>-of-pam4/

| 2023 Roadmap                                                      | 2019                                                                                              | 2020                                                                                | 2022                                                                            |                                                    | 2025                                                                                                                | 203                                                           | 0                                                                  | 2040                        |

|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------|

| Modules/TxRx<br>Data rate density<br>Form factor                  | 400Gbps<br>25 Tbps/1U<br>Q/OSFP                                                                   | 800Gbps<br>OSFP/QSFPDD/C                                                            | 100Tbps/1U                                                                      | 1600Gbps<br>Purple Brick Wall<br>Purple Brick Wall | 400Tbps/1U<br>OSFP/CoB                                                                                              | 1600<br>Micro-Co-Pkg,                                         | 3200Gbj<br>Tbps/1U<br>/CoB/OSFP                                    | 5                           |

| Typical link reach<br>Ind wish (@400Gbps)<br><i>Industry plan</i> | <10km<br>\$2/Gbps<br>>\$5/Gbps (<2km)                                                             | <10km <2<br>\$1/Gbps<br><\$2/Gb                                                     | Purple Brick Wall                                                               | \$0.5/Gbps                                         | <2km<br><i>\$0.5/Gbps</i>                                                                                           | <\$0.2/Gbps                                                   | <2km<br>\$0.2/Gbps                                                 |                             |

| Typical link reach<br>Ind wish (@400Gbps)<br><i>Industry plan</i> | 10-100m<br><\$1/Gbps<br>\$                                                                        | 5-50m<br><\$0.5/Gbps<br>1/Gbps                                                      | Purple Brick Wall                                                               | <\$0.25/Gbp                                        | 1-25m<br>\$<br>\$0.25;                                                                                              | <\$0.05/Gbps<br>Gbps                                          | <.                                                                 | \$0.15/Gbps                 |

| InP Monolithic<br>SiP & InP/SiGe hybrid                           | PIC WDM Tx & Rx (30G                                                                              | IRZ/PAM4-8<br>4" Wafe<br>100 devices<br>Purple Brick Wal<br>Hz) OEIC Int driver/TIA | NRZ/PAM4-16<br>r/fab 4 & 6"<br>1000 devices<br>70GHz (100Gbps<br>50Gbps (50GHz) | Purple Brick Wall Co<br>Wafer/fab                  | Purple Brick Wall<br>IC Int driver/TIA 10<br>herent client-side<br>Purple Brick Wall<br>ple Brick Wall<br>70GHz (40 | <i>8" W</i><br>10,000 devices<br>IGbps)<br>OEIC Int driver/TW | 100,000 devic<br>OEIC ASIC 500<br>'afer/fab?<br>A 100Gbps (serial) |                             |

| Polymer Photonics                                                 | 6" Wafer/fab<br>25GHz. 50GHz (Lase<br>PIC WDM/MZ Mod Tx &<br>NRZ/PAM4 & NRZ/PAM<br>3-4" Wafer/fab | Rx OEIC Int                                                                         | 8 & 12" Wafer/fa<br>100 devices<br>od)<br>driver/TIA (SiP/InP)<br>NRZ/PAM4-16   | 100GHz (1<br>50GHz OB                              | Pur,<br>Purple Brick Wall<br>50Gbps serial)<br>1C Int driver/TIA (S<br>herent client-side                           | 1000 devices<br>Purple Brick Wa<br>p/InP) 70GHz (serif)       | atijke Brick Wall OEIC                                             | 10,000 devxes<br>ASIC 70GHz |

| Dielectric Photonics                                              | 100 devices<br>25GHz. 50GHz<br>PIC Tx & Rx<br>NRZ/PAM4 & NRZ/PAM<br>6″ Wafer/fab                  |                                                                                     | Purple Brick Wall                                                               |                                                    | herent client-side                                                                                                  |                                                               | 100,000 devic<br>driver/TIA 70GHz<br>Wafer/fab                     |                             |

| GaAs (VCSEL)                                                      | 100 devices<br>25GHz. 50GHz<br>VCSEL PIC 25GHz<br>NRZ/PAM4 & NRZ/PAM<br>_6″ Wafer/fab             | Purple Brick Wall VCSEL PIC 50GHz Purple Brick                                      |                                                                                 | 10000 devices<br>Cd<br><u>8″ Wafer/fab</u>         |                                                                                                                     | 100,000<br>/CSEL-Mod)<br>0GHz (100Gbps)                       | devices                                                            |                             |

|                                                                   | Normal Black Font<br>= Reasonably expe<br>efforts                                                 | ected based on current                                                              | Pur<br>= Technology                                                             | ple Brick                                          | Wall                                                                                                                | Slanted Red Fo<br>= Major indus<br>commercializa              | try effort requ                                                    | ired for                    |

Sources: LWLG, Photon Delta, IPSR (2023)

*Figure 1: Transceiver/module roadmap showing purple brick walls for technologies that will drive transceiver design (Sources: LWLG, IPSR, PhotonDelta)*

Sources: LWLG, Photon Delta, IPSR (2023)

Figure 2: Transceiver/module roadmap showing the key challenges identified by the purple brick walls for technologies that will drive transceiver design (Sources: LWLG, IPSR, PhotonDelta)

Table 1. Purple brick wall barriers – critical needs for transceivers/modules

| Purple Brick Wall                   | Description                                                            |

|-------------------------------------|------------------------------------------------------------------------|

| Product vehicle                     | >3.2Tbps and 6.4Tbps optical transceiver using multichannels           |

| Form factor                         | Higher density and smaller form factor than OSFP today                 |

| Lasers                              | High operating temp (>150C); wavelength stable, uncooled 1310nm        |

| Low noise integrated opt amplifiers | Noise factors for optical amplifiers <5dB                              |

| High speed, low power modulators    | >100GHz 3dB bandwidth (EO); 1Volt or less for direct drive from CMOS   |

| Waveguide loss                      | Low loss in visible wavelengths <0.01dB/cm                             |

| Temperature of operation            | 0-85C uncooled                                                         |

| Power consumption of TxRx           | <1Tbps/10W                                                             |

| Full PIC implementation             | Includes both Active and passive integrated components on PIC platform |

### PURPLE BRICK WALL FOR OPTICAL INTERCONNECTS

The optical interconnects roadmap, shown in Figure 3, is organized into Product Vehicles, Metrics, and Technologies sections which are described below after the transceiver section. Unless stated otherwise, the event dates mark the year of commercial adoption. Table 2 summarizes the interconnect critical technology needs also known as the purple brick wall barriers.

|                     | 2023 Roadmap<br>Optical Interconnects                 | 2023                                                                    | 2025                               |                                                                                  | 2030                           | 2035                                                                                                              | 2045                        |  |

|---------------------|-------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

| es ct               | Pluggables                                            | Multi-fiber-to-fiber: N                                                 | IPO, MXC, MMC/TMT                  | Reflow Ferrules 80 um                                                            | MPO Purple Brick Wall SMF/PM   | IF multi-fiber ferrules/FAUs Multi-o                                                                              | core, multi-fiber ferrules  |  |

| Product<br>Vehicles | Co-packaging                                          | Pigtail FAU-to-PIC, act                                                 | ive alignment                      | Fiber-to-PIC connector                                                           | Purple Brick Wall PIC Flip chi | p Board-embedded waveguide                                                                                        | s 3D Integration            |  |

| Pro<br>Ve           | Intra-board/module                                    |                                                                         | PIC-to-Si/SiN interpose            | Purple Brid                                                                      | wall PIC-to-Glass interp       | poser PIC Flip chip C                                                                                             | CPU-to-HBM 3D Integration   |  |

|                     |                                                       |                                                                         |                                    | \$1 Purple Brick Wall                                                            | 40.00                          | 4                                                                                                                 | 40.10                       |  |

| S                   | Cost (\$/termination)                                 | \$2<br>\$2.5                                                            | 44.4                               | <b>\$1</b>                                                                       | \$0.65<br>\$0.5                | \$0.40<br>\$0.30                                                                                                  | \$0.13<br>\$0.1             |  |

| Metrics             | Loss (dB, max)                                        | •                                                                       | \$2.0<br>as needed to maintain 3 d | Ş1.04                                                                            | •                              | pp drives loss as low as possible                                                                                 | 50.1<br>≤ 0.25 dB           |  |

| Š                   | Manufacturing<br>Scale (term/yr)                      | 188M                                                                    | 290M                               | Purple Brick Wall                                                                | >1B                            | >4.3B                                                                                                             | >43B                        |  |

|                     | Fibers/V-grooves                                      |                                                                         | 80 um fiber                        | 80 um ribbon and V-gro                                                           | Purple Brick Wall PM Ribl      | bon, Reflow Optimized FAUs Multi-co                                                                               | re MDM Ribbon               |  |

| Technologies        | Waveguides                                            | Glass loss <0.1 dB/cm<br>Polymer loss <0.08 dB<br>PCB Integration of MM | /cm (@ 850nm) Poly                 | timized glass loss w/ <0.0<br>mer loss <0.1 / 0.2 dB/cm<br>PCB Integration of SM |                                | ent coupling < 1 dB Purple Brick Wall<br>optimized loss <0.1 dB/cm (all w<br>Purple Brick Wall<br>CPU/HBM interce |                             |  |

| lou                 | Expanded Beam                                         | 1 dB for 12 fibers, mar                                                 | nual termination 0                 | .75 dB for 16 fibers, semi-                                                      | automated termination          | Purple Brick Wall 0.5 dB for 32 fibers, automat                                                                   | ted termination > 64 fibers |  |

| sch                 | Alignment                                             | Active Optical                                                          | Active visio                       | n-based or connector                                                             | Purple Brick Wall Passive -    | semi-automated Passive                                                                                            | w/ High Speed Pick & Place  |  |

| μ                   | Attach                                                | Attach Manual - fibers in V-groove Purple brick Wall                    |                                    |                                                                                  |                                |                                                                                                                   |                             |  |

|                     | Architecture                                          | Fiber pigtail fly-over to                                               | o board edge Fil                   | per on-package connector                                                         | On-board connector?            | urple Brick Wall FTTS Package interposer far                                                                      | n-out PIC to board wg       |  |

|                     | Fiber-to-fiber<br>Fiber-to-chip<br>Chip-to-chip/board |                                                                         | ed based on current effort         | 5 = Technology co                                                                | ble Brick Wall                 | Slanted Red Font<br>= Major industry effort requi<br>commercialization                                            | ired for                    |  |

|                     |                                                       | A Optical I                                                             | nterconnects                       | Roadmap to                                                                       | oward low-cos                  | st OSAT scalability                                                                                               |                             |  |

Figure 3: Optical interconnect roadmap showing the key challenges identified by the purple brick walls for technologies that will drive optical interconnect design (Sources: TWG Interconnect working group, IPSR, PhotonDelta)

### Table 2. Purple brick wall barriers – critical needs for optical interconnects

| Purple Brick Wall        | Description                                                       |

|--------------------------|-------------------------------------------------------------------|

| Pluggable                | Next generation, small form factor connector                      |

| Co-packaging/intra-board | Flip-chip PICs w/ electrical and optical interconnects            |

| Cost                     | < \$1 per termination                                             |

| Loss                     | < 1 dB max                                                        |

| Manufacturing Scale      | Scaling to 1B terminations per year, intra-shelf fiber management |

| Fibers/V-grooves         | PM ribbon, reflow-optimized FAUs                                  |

| Glass Waveguides         | Electrical/optical heterogeneous board integration                |

| Polymer Waveguides       | XSR/USR optical interconnects                                     |

| Expanded Beam            | 0.5 dB loss for 32 fiber array, automated termination             |

| Alignment                | Passive – semi-automated                                          |

| Attachment               | Semi-automated – latching/mating                                  |

| Architecture             | Fiber-to-the-server costs                                         |

### TRANSCEIVER ROADMAP CHALLENGES:

Several vendors are looking at how to address 200G line rates, and are planning spatial multiplexing (adding fibers), wavelength division multiplexing, (adding wavelengths in a single fiber), encoding with more complex symbols per bit (PAM, QAM, etc.), designing optical and electrical devices for higher bandwidth, lower voltage (power), and smaller footprint (size) as part of a PIC platform. These higher performance drivers are being accelerated by data hungry customers such as data centers, high performance computing, and shorter reach telecommunications.

Yet the main roadmap challenge for the fiber communications industry is to plan future data line rates that exceed 200G and extend towards 300G and 400G. These line rates are needed to achieve pluggable transceiver and/or co-packaged transceiver aggregate data rates of 400Gbps, 800Gbps, 1600Gbps (or 1.6Tbps), 3200Gbps, 6400Gbps and beyond. While companies are looking to complete the designs for 200G line rates in the 2023-2025 timeframe, they are also looking how to extend the data rates and line rates further<sup>2</sup>. Interest in line rates of 300G and 400G are still at an early stage, however, active electro-optic polymers offer modulator device demonstrations today that achieve these goals<sup>3</sup>.

Processors, storage, networking and switching fabric performance, and their future trend toward increased integration, are all driving the packaging requirements for data centers. Whereas thermal, electrical, photonic and mechanical metrics constrain and direct development of that packaging. Of these, thermal and power management of the system continue to be major challenges for data centers. A key component of the total cost of ownership is the cost of the energy to power the high-end equipment. And, in some locations, the amount of energy that can be delivered to a data center is at the limits of what the electrical utility can deliver. To achieve reduced energy use, the American Society of Heating, Refrigerating and Air-Conditioning Engineers (ASHRAE) is creating standards where the temperature and humidity can be higher than has been traditionally required for high-end equipment. ASHRAE recommends that server inlet temperatures be between 18 and 27 degrees Celsius (64.4 to 80.6 degrees Fahrenheit), with relative humidity anywhere between 20 and 80 percent. While less energy is required to cool the data center, there is a need for better thermal technologies within these

<sup>&</sup>lt;sup>2</sup> Arista presentation from OFC 2022 for OSFP pluggable optical transceivers

<sup>&</sup>lt;sup>3 3</sup> <u>https://www.lightwavelogic.com/presentation/polymer-modulators</u>-with-<u>50ghz-performance-for-power-consumption-reduction-at-400-</u>800-and-1600-gbaud-aggregated-datarates

systems to maintain acceptable junction temperatures.

Likewise, active power management of individual components to maximize the power performance of the system is also a desirable capability. More efficient power conversion will also continue to be developed including voltage regulation close to the loads (such as in microprocessors) that significantly cut the power distribution losses within the system.

Packaging technology must also increase at a rapid rate to achieve the new performance requirements. As breakpoints are reached, lower loss laminates, smoother copper, and higher bandwidth connectors are required. Development of these components in high-volume manufacturing with cost-competitive materials and processes is ongoing. The reader is encouraged to read the Packaging and Assembly roadmap chapters for further details.

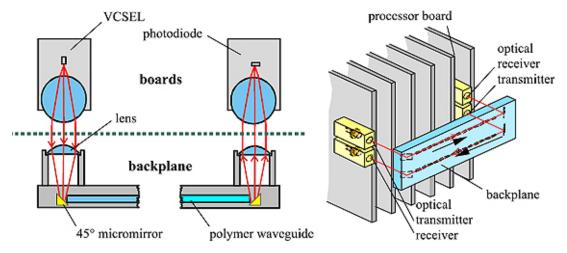

Optical interconnects are becoming more widely used with VCSEL data rates reaching 50 Gbps and silicon photonics becoming commercially viable. The need for increasing bandwidth to move the data as well as the growing size of data centers defining the distance the high bandwidth interconnect must travel is creating more need for optical communication. At this time 3 meters has the potential to be the breakpoint between copper cables and optical fibers, but this is expected to fall to 2 m and 1 m over the next decade. As aggregated data rates surpass 400 Gbps, and increase to 800 Gbps, and even 1600 Gbps, on-board photonics (i.e., printed circuit board) and more likely on-package photonics (i.e., co-packaged transceivers and electric chips on the package substrate) will be required.

However, the biggest challenge is transmitting ever increasing data streams with minimal latency to keep up with computational demands. With processor clock frequencies stagnated, data centers are designed as CPU/GPU clusters with all-to-all compute server access and ultimately disaggregation of compute, memory, and storage. Disaggregation requires ~10 ns CPU-to-CPU access and ~20 ns CPU-to-memory access which runs counter to the added latency (and increased power) of digital signal processing necessary to clean up electronic signals to maintain their integrity. Optical transmission which doesn't need this high level of signal conditioning encourages the move toward optical off-die data input/output. And while optical transmitter and receiver designs are driving power requirements down, adding more lanes/channels to increase bandwidth is limited by the expectation of decreasing price and overall power. This results in the current trend of quickly increasing data rates per physical channel.

As an aside, analog pre-emphasis as a low power equalization technique has been highly effective in boosting the bandwidth and data rates of VCSELs to 50 Gbps. While individual VCSEL transmission systems are composed of discrete components, arrays with combined functions are considered as integrated photonics particularly within the manufacturing scale interconnect terminations per year section of this report. Note that current VCSEL transmission systems are multimode and limited in distance by the chromatic dispersion of multimode fiber. For example, OM5 fiber has an effective modal bandwidth of 4700 MHz\*km at 850 nm wavelength of operation or 100 meters of 100GBASE-SR4.

The above energy limiting factors in addition to efficiency, latency, and the growth of data transmission, place a challenge on the processing power needed to perform any data analytics because the total available power is split between the processing or compute power and the networking or transmission power between the processing units. Instead of adding general-purpose cores to a chip and enabling those cores to support additional threads, an emerging trend, perhaps more efficient, is to employ specialty cores to do specific tasks. The use of GPUs and FPGAs allow quick turn-around time to quickly adopt more compute and energy efficient algorithms while special ASIC cores are developed to address specific computational tasks. As the big-data era matures and 2 and 3 nm silicon nodes are developed, the packaging technologies to interconnect these components will also evolve. The challenge is to keep the momentum of scaling performance with cost, as the price of designing using 10 nm (or less) silicon nodes is becoming higher.

### TRANSCEIVER TECHNOLOGY NEEDS

Data bandwidth demand is resulting in systems with ever faster interconnect speeds, even as processor speed is staying constant. The enormous size of the hyperscale data centers creates a huge demand for electrical power and an increasing focus on power efficiency. So, data center operators try to reduce power consumption and operation costs to manage the total cost of ownership. PIC-based transceivers as the low cost and low power solution have become the dominate solution at 500 meter intra-data center distances and are looking to expand to shorter, 100-meter high-performance computing, and longer, 2 km, campus-wide reaches.

Photonic packaging technology must create disruptive solutions to achieve the new performance requirements, in particular faster photonic devices such as 100 GHz modulators that can operate at 100 Gbps NRZ or 200 Gbaud PAM4. Today, one technology close to meeting these speed metrics with low power consumption are polymer modulators<sup>4</sup>. There are other modulators that are being developed with both the potential for high speed and low power that include: slot modulators, plasmonic slot modulators, silicon-based GeSi EAMs, micro-rings, Barium Titanate (BTO), and thin-film lithium niobate.

Data centers need faster optical devices (such as 100+ GHz components), higher integration levels, higher reliability, lower power consumption, a higher degree of scalable economics that address \$/Gbps metrics, and smaller, more miniaturized foot-print platforms. Co-packaged solutions with hybrid integration between different technologies are also required. The integration of electronics, photonics, and packaging is an important topic that the industry will explore more intensity over the next decade.

#### Needs 2025

- Device speed increased (modulator bandwidths EO S21 of 100 GHz in PIC platform

- Drive voltage at 1V so that drivers can be eliminated to enable linear drive optical architectures.

- Co-packaging of electronics and photonics, OSFP and QSFP-DD lower power designs

- Hybrid integration of InP lasers with Si photonics

#### Needs 2030

- Device speed increased (modulator bandwidths EO S21 to 150 GHz+ in PIC platform

- Laser operation uncooled to >100 °C

- Reduced power consumption (50% reduction), with architectures such as Linear Drive Optics

- Integration of photonics and electronics

#### Needs > 2040

- Device speed increased (modulator bandwidths EO S21 to 200 GHz+ in PIC platform

- Laser operation uncooled to >150 °C

- Reduced power consumption (80% reduction), with architectures such as Linear Drive Optics

- Further integration of photonics and electronics

- Uncooled coherent laser with better than 2 GHz stability

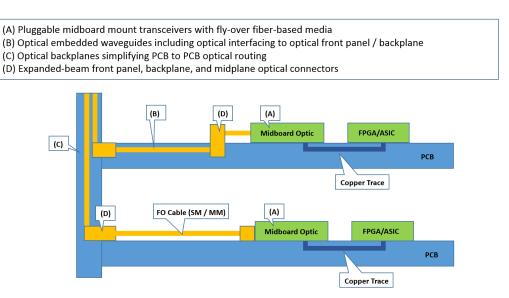

### INTERCONNECT PRODUCT VEHICLES

Product vehicles are organized by packaging architecture, not application reach. Application areas are described in the Appendix's Situational Analysis section.

<sup>&</sup>lt;sup>4</sup> <u>https://www.lightwavelogic.com/presentation/polymer-modulators</u>-with-<u>50ghz-performance-for-power-consumption-reduction-at-400-</u> 800-and-1600-gbaud-aggregated-datarates/

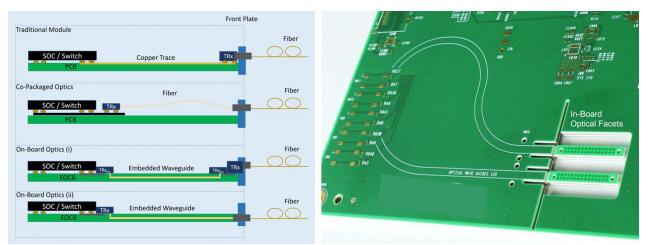

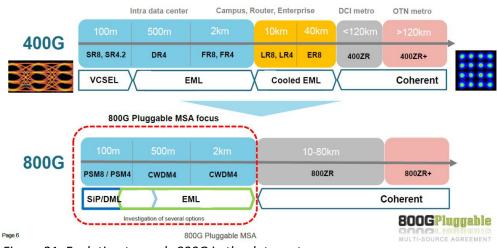

## PLUGGABLES AND CO-PACKAGING

Optical interconnects in data centers, either between Ethernet switches or between switches and servers (i.e., highpowered computers), are created with transceivers at each end of an optical fiber link where the fiber between equipment racks is known as structured cable. Today, transceivers are available in numerous form factors (e.g., QSFP, OSFP), defined by multi-source agreements (MSAs) and IEEE standards, and plugged into the front panel of a server or switch shelf within a data communication rack. These "pluggable" transceivers have numerous benefits: ability to mix & match depending on customer need (e.g., choose right data rate for each individual modules); low cost due to MSA "standardization"; modularity for pay-as-you-grow economics; hot swappable for easy adds/changes and repair; and ever-increasing bandwidth within the same mechanical envelope. [3] And the industry has a path to 1.6 Tbps data rate with the recently announced OSFP-XD MSA staying with current and therefore less risky 100G optics and 16+16 I+O channels putting the speed increase burden on increasing the number of parallel channels. [4] [5] Yet signal integrity across the printed circuit board (PCB) electrical transmission lines from the server or switch to the front panel has become very challenging as the electrical interconnect data rate doubled from 28 Gbps, NRZ (non-return to zero modulation format) to 56 Gbps and now 112 Gbps, PAM4 (four-level pulse-amplitude modulation format). [6] Increased forward error correction (FEC), transmitter equalizer pre-emphasis, and receiver digital signal processing (decision feedback equalization, DFE, and/or feed-forward equalization, FFE, and continuous time linear equalizer, CTLE) overcome loss from electrical signal impairments like loss from the skin effect and radiation, multi-path interference (MPI) from impedance mismatch reflections, and crosstalk from neighboring channels. But this is at the expense of higher power consumption (more than 50% [6]) and resulting thermal dissipation. The benefits of co-packaging are so great that optical engines are even becoming available for previously released 25.6T Ethernet switches. [7]

Since the OIF's 112G VSR PAM4 CEI IA (Optical Interface Forum's Very Short Reach Common Electrical Interface Implementation Agreement) specifies a 20-cm reach across the PCB which is not quite sufficient for the full wide of the 19" front panel, the latest 51 Tbps switches use more power hunger LR SERDES (long reach, serializer/deserializer) with 1 meter reach. [8] The LR SERDES allow for a 100G PAM4 interface to direct attach copper (DAC), front panel pluggable optics, and/or co-packaged optics, but consumes far more power than switch ASICs likely to be introduced in the next generation that should be optimized for co-packaged optics with VSR SERDES. In other words, the power consumption required for electrical signal integrity is motivating the move to co-packaging the transceiver (stripped down as an optical engine without the mechanical envelope) on the same package substrate as the Ethernet switch ASIC and the use of VSR or even XSR SERDES, resulting in 50% lower power consumption down to below twenty or even ten pico-joules per bit. [6] [7] While this is a huge benefit, issues are currently being resolved with yield, rework, reliability, concentrated heat generation, and establishing a robust supply chain including the role of OSATs. While the roadmap refers to Ethernet switch ASICs within data centers since this is the initial off-chip bandwidth driving application, in the future many other high bandwidth ASICs such as FPGAs (e.g., for direct-RF sampling massive MIMO) [9] and CPUs/GPUs for artificial intelligence will rely on copackaging. In fact, co-packaged optics (CPO) specifically designed for AI/ML has been announced with direct drive from the host ASIC SERDES to the CPO. [10]

Incumbent pluggables and emerging co-packaging optics (CPO) are and will continue to be similar in PIC footprint and channel count since transceiver companies will want to develop the same PIC for both applications. At present, the difference is in the length of fiber ribbon jumper between the FAU attached to the PIC and the outside world: ~1 cm from PIC-to-pluggable front plate; ~30 cm from PIC co-package optical engine to the shelf front panel. Besides jumper length, another difference for co-packaged PICs supplied with external lasers are fibers (typically polarizationmaintaining) from external laser sources to the PICs. Various options exist for external laser source delivery to the CPO. [11] Pluggables have either internal lasers or micro-optic beam delivery. Co-packaged optical engines could move in this direction too if high-temperature laser operation can be achieved which is on the transceiver roadmap.

Since the pluggable face plate is somewhat more space constrained than the pass-through front panel connectors

of CPO, it is anticipated that pluggables will drive the connector cross-sectional space saving innovations that joints the pluggable fiber jumper to the outside-the-box fiber and that then it will be adopted to the CPO front panel application. Recently introduced MCM connectors with TMT ferrules offer the highest density, commercially available 1x16 or 2x12 fiber with 250 micron pitched MPO-type connectors. Since 80-micron diameter fibers are available, the next logical step in density could be developing fiber ribbon that when interleaved provides 125/127micron pitch in a molded ferrule connector. Ultra-small connectors that require tools for installation rather than a human hand are another logical step but require industry consensus which has proven to be difficult. Beyond ~2035, increased space-division multiplexing I/O density within a standard molded ferrule connector can probably only be solved with multi-core fibers (MCF) or, less likely, mode-division multiplexed (SDM) few-mode fibers. Rotational orientation of a single multi-core fiber within a V-groove to align cores ~25 microns in pitch is commercially available and it has been demonstrated in fiber connectors. The purple brick wall challenge is the efficient orientation of multiple multi-core fibers. Fiber ribbon makes molded ferrule and V-groove fiber assembly efficient but individual fiber orientation within the ribbon is extremely difficult due to current processes. While MCF in short reach applications avoids the complication of amplification, depending on network architecture, it may need fan-outs from MCF to individual fibers. This adds cost and loss unless somehow integrated within the photonic circuit. Hence the best use of MCF if it can be ribbonized is in point-to-point links that reduce space particularly in structured cable overhead trays if the fanout can be integrated in the PIC. An implication is the need for a linear, not hex-packed, core geometry.

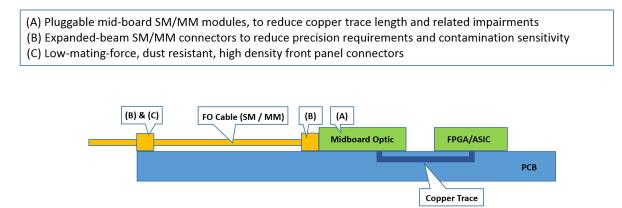

For co-packaging with typically 16 optical engines surrounding a central switch ASIC, [6] fiber management schemes and designs for physical separation (optically, electrically, or both) are critical. See the reference for a more complete description of options and tradeoffs. [11] Adhesively-bonded FAUs are manageable in the first generation but detachability along with latching is highly desirable for package-to-board assembly & rework, e.g., solder reflow and fiber routing. A recent announcement of a PIC connector in development, could mean ~2025 for commercial availability, assuming a 2- to 3-year development cycle. [12] Expanded beam optics (EBO) are also in the running and being actively developed. [13] [14] At some point, perhaps once more than one fiber ribbon connector per optical engine is required, more advanced fiber management schemes could include on-board connectors and ultimately a drive toward embedded waveguides and routing within, or on top of, the PCB.

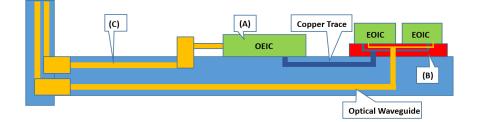

The next likely development is flip-chip assembly of PICs for the benefit of efficient electrical interconnect packaging. Initially there may not be any change to optical interconnects but to take full advantage of the assembly efficiency, developing optical coupling either to, or on top of a package substrate interposer will be necessary and require significant technical development (hence a purple brick wall event). Interposers increase the available optical I/O shoreline by accessing the edge of the interposer rather than the PIC and, for the right dimensional-stable materials, can provide a dimensionally stable surface with alignment elements for passive fiber array alignment. In fact, the optical IO shoreline could be greater than that provided by a substrate with electrical vias to the BGAs attached to the PCB in a cantilevered design. Hence a glass package interposer substrate is on the roadmap prior to board-level waveguides. Eventually, as stated above, embedded glass waveguides within the PCB or specialized interposers are likely a solution to keep up with the ever-increasing number of PIC channels needed due to relentless switch ASIC bandwidth doubling every two years. Already, the number of fibers is 1024 for DR-based 51 Tbps switches. Interconnect routing will be simplified with low-loss glass waveguides once efficient, low loss coupling to those waveguides is developed. Polymer waveguides, on the other hand, which could have a play at shorter reach, probably are too lossy for routing to the front panel unless used at 850 nm wavelength for low-loss propagation and having e-o and o-e conversion at that wavelength within the board. And finally, in the roadmap in the distance future is included some type of 3D interconnects (to be determined) for stacked PICs and PIC to board-level waveguides. This prediction is consistent with existing 3D electrical IC stacking and corresponding through silicon via interconnects.

### **INTRA-MODULE AND INTRA-BOARD**

The timing of optical intra-board (or intra-blade) and intra-module (or intra-package) products is expected to be delayed by incumbent electrical solutions. Electrical board-level VSR, XSR (extra-short reach), and USR (ultra-short reach) transmission line interconnects have standards and products at 100Gbps and working groups exploring 200Gbps channels. Electrical transmission across PCBs increasingly requires more power-hungry digital signal processing up to and including retimers but its cost is at least an order of magnitude lower than the optical alternative. Also, electrical fly-over cable within greater bandwidth capacity is a viable solution to further delay optical intra-board interconnects. The trigger for adopting optics within data center rack shelves will be driven by co-packaging fiber management problems. Once there are PCB-embedded optical waveguides and associated low-loss, low-cost, and scalable package-to-board optical coupling solutions available for switch-to-front-panel CPO interconnects but not necessarily at cost parity. Full system-level cost-of-ownership costs that include electrical power consumption and heat management will likely hasten adoption once technical solutions are fully developed and are released into the market.

While the transition to optical interconnects from electrical interconnects has followed a continuous path of evershorter reach as the distance or reach times bandwidth product exceeds ~100Gb-m/s, that trend looks to be disturbed by the emergence of chiplet technology and heterogeneous integration. The demand of artificial intelligence for compute power necessitates closer/tighter packaging of compute chips like CPUs, GPUs, VPUs, Accelerators, FPGAs, ASICs

and memory (e.g., stacked DRAM). Multiple chips (e.g., up to 16) on a single multichip module (MCM) with high bandwidth, low latency interconnects addresses this need. Yet electrical interface standards such as High Bandwidth Memory (HBM), Advanced Interface Bus (AIB), and Universal Chiplet Interconnect Express (UCIe) struggle to provide the needed bandwidth (>2 Tbps), over the MCM substrate reach (>50 mm), at low latency (<20 ns) and power (<5 pJ/b). An approach that disrupts the gradual transition to optical interconnects could use of one of these standards from the chips to an optical transceiver engine followed by optical transmission across the MCM substrate and subsequent optical-electrical conversion and electrical transmission to the receive chip. The remaining challenge is low-loss, low-cost, scalable PIC transceiver to substrate coupling. This is an active R&D area and even the availability of an early commercial solution. [Lightmatter Passage brings Co-Packaged Optics and Silicon Photonics to the Chiplet Era (servethehome.com)]

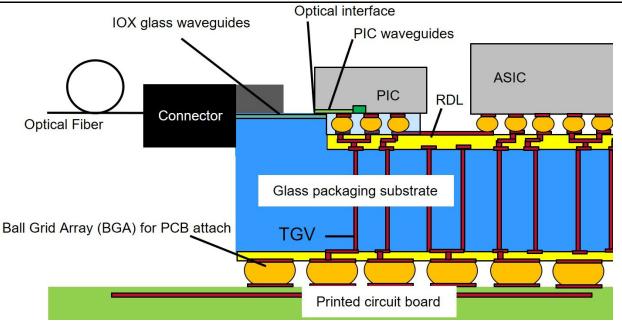

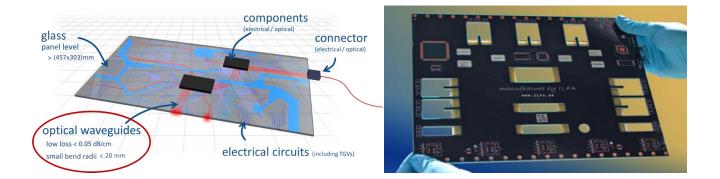

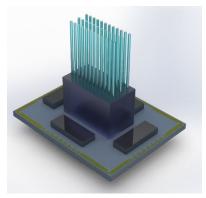

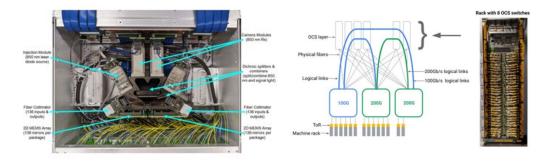

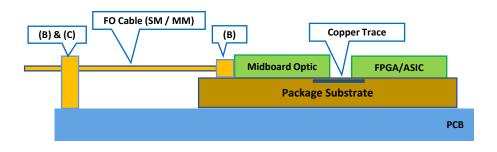

The purple brick wall graphic lists events in the year of general commercial adoption not in technology development, a press release, conference demonstrator, or limited/general commercial availability. The exception is intramodule/board where the next several years is not expected to have commercial traction (hence the text prior to 2028 is grayed out). Events prior to that such as PIC-to-SiN interposers may be adopted for co-packaging but will be technology building blocks for the eventuality of optics displacing copper at these ever-shorter reaches. Using history as a guide, that should occur for intra-board, ~50 cm reach, once data rates exceed 200 Gbps, for a 100Gbps-m, distance times bandwidth product (aside from the MCM interconnects described previously). PIC flip chip will improve assembly manufacturing scale but needs significantly more process development to work out the optical I/O and come to fruition (example shown in Figure 4). While board-embedded waveguides could be beneficial with on-board connectors combined with short PIC-to-board jumpers, the combination of embedded waveguides and PIC flip-chip will likely be needed for intra-board optical interconnects to be viable. For optical interconnects to displace electrical transmission lines within the package, e.g., for CPU-to-stacked high bandwidth memory, optical engines will probably need another order of magnitude drop in cost. An intriguing alternative is micro-LEDs that today are widely used in display applications. [15]

Figure 4. Example of a PIC flip chip onto glass package substrate with evanescent optical coupling interconnects to ion-exchange glass waveguides on the package surface and through glass via (TGV) electrical interconnects through the package to the PCB. [16]

## **KEY METRICS**

## **COST (\$/TERMINATION)**

The most important metric is cost (meaning end customer price) since it heavily influences the buyer's decision. More specifically, what drives technology adoption is the total cost of ownership for the dominant player within the value chain. In the case of PIC interconnects, that is the hyperscale data center operator. Total cost of ownership is capital costs plus operating costs and the conversion costs for adoption if it is a new technology. New technology comes with unforeseen risks, so the adoption barrier, real and perceived, needs to be overcome by a strong value proposition.

As the PIC chip costs are driven down by foundry volume scaling, and testing costs are driven down by automation and sampling, the optical interconnect costs will come under increasing pressure. And for new PIC sensing and imaging applications, which tend to be more price sensitive, that cost pressure is even stronger. But only so much cost reduction comes from volume scaling of data center interconnects and adopting them to more price-sensitive PIC applications.

Cost is a notoriously hard metric to quantify given companies' reluctance to share this sensitive information. Additionally, any outside cost model requires a multitude of estimates and assumptions within the categories of bill of materials, labor costs, equipment costs, overhead costs, and profit. An attempt at quantifying the price of MPO and FAUs has been made for this roadmap; MPO and fiber array unit costs are obtained through quotes and the internet. However, the numbers are intended to be for guidance and directionally correct and not based on any specific company.

To begin, a current internet search finds that, in single quantities, 12 fiber MPO jumper prices range from \$25 to \$50 and 24 fiber MPO jumper prices range from \$50 to \$100 with both being \$2 to \$4/termination where termination is defined as the PIC-to external waveguide joint, in this case an optical fiber. Volume ordering should decrease the

### **IPSR-I DATACENTERS & TELECOM**

unit price counter-balanced by the desire to buy at the upper end of the price range due to quality concerns from the high labor costs and risk of the jumper not working in a large installation. Hence the fiber-to-fiber termination price on the purple brick wall is assumed to start at \$2/termination. This also assumes that installation costs are negligible with just a few seconds to clean and make the connection. Of course, customers will demand cost reduction over time, perhaps 5-10%/year. Additionally, higher fiber count interconnects, 2x12 and 2x16, with potentially similar assembly costs should drive a 2X reduction over the short-term time frame. Beyond the next several years, lower costs from such a well-established, incumbent technology will need to come from automation. Volumes will need to justify any capital expenditures for automation equipment and are expected to do so with the growth of artificial intelligence and the need for computationally intensive training algorithms. A purple brick wall event demarks manual-to-automated conversion due to the complication of converting intricate manual assembly to semi- and then fully automated assembly, particularly fiber loading into the MT ferrules, along with the unknown market timing of when volumes justify that conversion. Pricing on the purple brick wall assumes a 2X price reduction in 2026 due to 2x greater number of channels within the MPO interconnect at the same price and 10% per year reduction after that.

By contrast, fiber-to-chip termination is dominated by fibers loaded in glass V-grooves and actively aligned to the PIC for edge coupling. The bill of materials is expected to be greatly reduced over a full MPO connector, but the active alignment and particularly bonding/curing time adds significant time on an expensive, 6-axis alignment machine. A recent price quote for 1-9 quantities of glass V-groove fiber array units is ~\$16/termination. This is much higher than a volume (~1M unit) price target estimated at ~\$1/termination. On top of this, the attachment and bonding are estimated to be \$1.74 if manufactured in the US and \$1.34 if manufacturing in a low-labor country. Assumptions include 5-year depreciation on a 6-axis active alignment tool, 5-minute tact time, 2 working shifts per day, 76% machine up-time (accounting for maintenance, repair, plant shutdown, and daily overhead), 12 terminations per unit, and 100% cost-to-price markup (for profit, SG&A, R&D, taxes, utilities & space, and repair & warehousing). Under the assumption that production starts in the US and moves to a low-labor country halfway through the depreciation cycle, the current estimated attachment cost on the purple brick wall is \$1.50. Hence the total unit plus attachment price starts at \$2.5/termination.

Given that the incumbent V-groove technology is more than 30 years old, opportunity for cost reduction is limited. Production efficiency, minimizing CAPEX, and low-labor market production should keep a 5-10% price reduction going in the short term. While many new approaches are being explored longer term, none have emerged as the clear winner. Hence a purple brick wall event is anticipated which will get resolved through the hard work of yield improvements upon manufacturing scale-up and rigorous reliability testing of a new, winning technology. A large drop in price should occur, placed in the late 2020s, and after that subsequent 5-10% price reduction.

Over time, glass V-grooves may migrate to silicon V-grooves on the PIC or interposer (particularly for quantum, cryogenic applications), before moving to either evanescent coupling or expanded beam coupling (from the edge or surface). Alignment may evolve into vision-based and then passive alignment. Assembly will likely migrate to semiautomated, then automated, and ultimately full compatibility with the silicon electronic industry's OSATs (outsourced semiconductor assembly and testing) and traditional high-speed pick & place tools. This should keep the \$/termination at an ever-decreasing level such that termination does not begin to dominate the packaged PIC cost and maintains its relative percentage of the total package cost.

## **COUPLING LOSS**

Insertion loss (in dB) is the attenuation between two fixed points in an optical system and for this roadmap is the worst-case manufacturing distribution over the transceiver operating temperature and lifetime. For pluggables, the two points are between the PIC waveguide just before the input/output terminus and the pluggable-side connector interface (PIC-to-fiber coupling loss plus negligible fiber propagation loss from a short (~1 cm) fiber jumper); for co-packaging, the two points are between the PIC waveguide just before the input/output terminus and the front-panel side connector interface (currently PIC-to-fiber coupling loss plus a bit more fiber (<0.5 meter) but still negligible

fiber propagation loss). This definition ensures compliance with the IEEE 802.3 3 dB link budget for 500-meter reach, low-cost transceivers. SiP has been able to meet this standard and due to integration cost benefits has become the preferred transceiver.

Coupling loss (pluggable or co-packaging) has contributions from mode converters (if used), mode-field diameter mismatch, and alignment error between the PIC waveguide and the fiber. For edge coupling, inverse tapers of the silicon waveguide expand the mode field to nearly that of single mode fiber. It especially works well if a top layer of SiN is used as an intermediate coupling medium and/or a thicker 3 micron buried oxide layer is used. Active alignment with precision 6 axis tools minimized any error resulting in coupling loss about as low as possible for any existing technology. Any incremental improvement for actively aligned edge coupling, while not expected, could help the yield hit for transceiver output power and result in lower transceiver cost. Passive alignment will provide scalability but the gap in coupling loss performance between active and passive needs to be closed (e.g., ~0.7 dB [6]).

In the future co-packaging insertion loss will include any intra-rack connectors and any PIC-to-interposer coupling and propagation loss. This is not a problem for first-generation coupling technology being commercially introduced which uses actively aligned, fiber array flyovers to front panel connectors. Yet any new technology to address cost, manufacturing scale and deployment speed must maintain this low insertion loss or push for a new standard that adds link budget, e.g., new technologies like connectors or other passive alignment in the intermediate term and fiber- or interposer-to-board-level waveguides to address fiber management in the longer term.

But by 2045 if not before, the accessibility of very low-cost SiP PIC transceivers there will be a desire for inter- and intra-rack link budgets to become the same. Additional waveguide propagation loss will make this a significant challenge and more likely will be met with shorter intra-board or inter-module reach than longer inter-rack optical backplane reach. The end result is that fiber-based optical backplanes are much more likely than waveguide-based ones.

For quantum applications, coupling loss needs to be as low as possible (e.g.,  $\leq 0.25$  dB). Every entangled photon quantum bit is valuable; loss of it requires retransmission, greatly impacting the data rate. An added requirement is operation near 4K so alignment at room temperature with a different fiber pitch-defining host material will have significant movement at the operating temperature due to coefficient of thermal expansion (CTE) mismatch and thermal walk-off. Hence silicon V-grooves with no thermal walk-off alignment errors are appropriate but a highly reliable solution to strain-relief of the fiber ribbon to the silicon V-groove is needed [17] and post-bond positional shift needs to be minimized. Another need is fiber with much better geometry specifications (cladding diameter and ovality, and core-clad concentricity). Fibers exist today with much better dimensional control than the standard single-mode fiber SMF-28 specification. Innovations in quantum PIC coupling, particularly tighter fiber geometry could be adopted for datacom as volume increases and price drops.

For some sensor applications, the sensing transducer is a disposable component separate from the source/detector PIC. Extremely low coupling cost and the need for rapid install/deinstall may afford a higher coupling loss specification.

### **DENSITY – LINEAR AND AREAL**

Switch ASIC bandwidth has been consistently doubling every two years putting a real strain on optical transceivers to keep up with a combination of increased channel count, more wavelengths, and/or more modulation levels. Historically, increased channel count is initially the low-cost solution and then newer transceiver generations at the same data rate increase wavelengths and/or modulation levels. The new OSFP-XD MSA for 1.6 Tbps pluggables follows that tradition but does not yet constrain linear, shoreline (PIC edge) density. It will not increase until the PIC waveguide layout consumes the entire PIC edge. With an assumed 10 cm edge and 127-micron pitch to match that of the fiber allowing for more than 64 parallel channels, it is not expected for the foreseeable future. If needed, 80-micron fibers interleaved in V-grooves provide a 50% density improvement. Other solutions are interposer fan-outs

and 2D surface coupling. Finally, in the long term, coherent transceivers could be the disruptor for 500-meter DC interconnects that further mitigates increased density requirements due to much better spectral efficiency with the QAM modulation format. The recent commercial release of 100ZR QSFP28-DCO (digital coherent optic) SiP transceivers for up to 100 km is significant in getting to a compatible pluggable form factor with less than 5 W power dissipation including DSP but costs will also need to drop significantly to be competitive to direct detection SiP transceivers. [18] The summary is that density, while an important design consideration, is not likely to be a critical constraint so is not represented on the purple brick wall.

## MANUFACTURING SCALE (TERMINATIONS/YEAR)

The relentless growth of the internet and the strong emergence of artificial intelligence and machine learning will be mirrored in the number of PIC-to-outside world input/output (I/O) terminations. As of 2023, there are 5.3 B internet users, three times the number of connected devices than the global population, and 14.7 B machine-to-machine connections. [19] Additionally, ~85% of data remains local East-West traffic within data centers and new AI-specific interconnect architectures will power PIC transceivers and resulting lane/channel terminations well into the future.

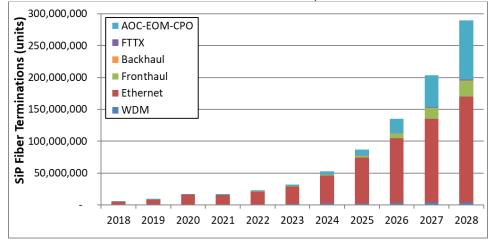

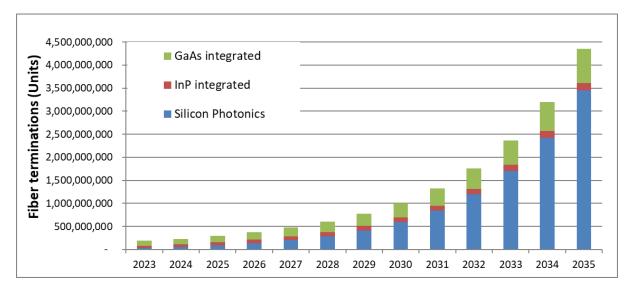

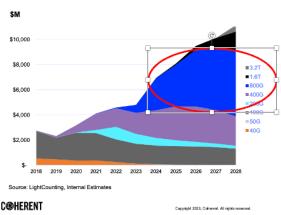

Terminations per year are based on market report volume and forecasting from 2018 to 2028 for the various GaAs, InP, and SiP integrated transceiver types (defined broadly as transceivers with at least two integrated functions). [20] Transceiver volume is converted to the number of terminations, (e.g., 8 terminations, Tx + Rx, for PSM4 and DR4). Then data was extrapolated to 2035 based on the individual material system's growth rate from the last year of the forecast, 2027 to 2028 of 42%, 8%, and 19% for SiP, InP, and GaAs material systems, respectively. Transceiver markets include wavelength division multiplexing (WDM), Ethernet, Fiber Channel, front haul, back haul, fiber-to-the-x (FTTx), and active optical cable/electro-optic modules-co-packaged optics (AOC-EOM-CPO) with Ethernet being by far the largest at 80% of terminations in 2023. The breakdown by market for SiP is shown in Figure 5. The terminations/year split by material systems in 2023 is 17%, 27%, and 56% out of a total 188M terminations for SiP, InP, and GaAs, respectively. However, SiP, InP, and GaAs growth rates over the next 5 years of 55%, 12%, and 16%, respectively, changes the mix to 48%, 15%, and 37% in 2028 (601M total terminations) and 79%, 4%, and 17% in 2035 (4.3B total terminations). This is due to the growth of SiP 500-meter 400G DR4 transceivers, followed by SiP 500-meter 800G DR8 and SiP 500-meter 1.6T DR8 transceivers. For example, 800G SiP terminations outpace 400G for all SiP transceiver types in 2027. SiP terminations dominate because they are the preferred transceiver type for 500-meter reach and 500-meter reach is the sweet spot for rack-to-rack DC interconnects.

Figure 5. Fiber terminations by year for SiP transceivers by market segment

An extrapolation of the year 4 to year 5 material type growth rates to the 5-to-10-year range is uncertain but should be directionally correct. That uncertainty comes from the transition from pluggables to co-packaging, timing and product mix of 3.2T transceivers, market adoption of fiber-to-the-server, and an unclear path beyond 200G PAM4 optics. Historically, the first generation of a higher speed transceiver occurs with more parallel

### **IPSR-I DATACENTERS & TELECOM**

lanes/channels followed by increases in wavelength, modulation speed, and/or modulation level. Increased parallelism is expected for 3.2T since both FR8 and PAM4 are built into the 1.6T data rate and more than 8 wavelength and 4 levels has significant technical challenges. Nevertheless, 3.2T transceivers with an expected 2X more terminations in their first generation are not reflected in the data even in the out years because there is no significant volume expected in the 5-year time horizon used for extrapolation. This reflects a conservative approach to the projections. Beyond 10 years, the number of terminations may dramatically increase as board-and module- level interconnects come into play. Perhaps a 10X bump at this lower level of interconnects can be expected but with the termination characteristics radically changing with flip-chip surface mount and high-speed pick & place technology. This 10x increase is reflected in the 2045-year terminations projection of the interconnect's purple brick wall.

Figure 6. Fiber termination by year for the three material system transceivers

### **INSTALLATION SPEED**

Installation speed becomes increasingly important with terminations per year growing from 188M today to 4.3B in 2035. Even for the unrealistic scenario of 24x7 installation, that translates to 6 termination/second across all manufacturing lines increasing to 138 termination/second. Clearly the assumed 5-minute current tact time for fiber array placement and bonding will struggle to scale - more tools in parallel is insufficient. Yet the recent announcements of co-packaged PIC-to-fiber connectors in development and accounting for a 2-year development cycle prior to commercialization, installation speed should have a dramatic drop in about 2025 to 10s of seconds, accounting for a connector cleaning step. The next jumps in installation will come first from semi-automated connector assembly and placement on the PIC with manual loading and unloading, then to full automation, and finally high-speed pick & place, flip-chip connections. While the interconnect's purple brick wall lists installation speed as the metric, a key installation challenge for fiber jumpers is fiber handling. A second further out is attachment consistent with pick & place tooling. Additionally, pick & place placement speed is highly dependent on required placement accuracy. Micron-level accuracy is needed for single mode insertion loss requirements. Technologies will need to be developed to provide alignment features or other mechanisms to translate the 5+ micron alignment accuracy of standard high-speed pick & place tools to micron level. Alternatively expanded

beam connectors relax the translational alignment tolerance to levels already available in standard pick & place tools.

### OPTICAL INTERCONNECT TECHNOLOGY NEEDS

## **FIBERS/V-GROOVES**

Fiber arrays in glass V-grooves (fiber array units, FAUs) have been commercialized for over 25 years and are the prevailing approach to multi-lane PIC I/O (either edge or grating coupling). They are highly reliable and provide low loss for matched mode field diameters on both sides of the interface ( $\leq 0.15$  dB). Fibers, often in 12-fiber ribbons are stripped, cleaned and placed within V-grooves machined into a small glass block by a computer numerical control (CNC) machine. The assembly is completed by epoxying the glass lid/cover to the fiber array and the fiber ribbon to the glass block for strain relief, followed by dicing, and grinding/polishing the front surface, either flat or angled. The other end of the fibers can be bare pigtails or connectorized. Various fiber types including the addition of individual polarization maintaining fibers are available. The glass material choice allows for a coefficient of thermal expansion (CTE) closely matched to silicon to minimize thermal walk-off of the fiber pitch over the device operating temperature range. The standard fiber pitch is 127 or 250 microns with 127-micron pitch achieved in standard 250-micron ribbon by interleaving two fiber ribbons. While arrays up to 96 are available, accuracy degrades:  $\pm 0.5$  microns for  $\leq 16$ ;  $\pm 1.0$  microns for  $\leq 48$ ;  $\pm 1.5$  microns for  $\leq 96$ . Fiber cladding diameter and ovality, and core-clad concentricity contribute to positional uncertainty independent of array size whereas translational error of the CNC tool accumulates with distance. It is conceivable that in the future displacement measuring interferometry could be applied to improve tooling positional accuracy. Such measurement systems can detect movement down to 1 pm but other sources of error besides those of the fiber may still make it challenging to have the same positional accuracy independent of array size. Besides, the warp of the PIC chip from its thermal history and material layer CTE differences serves as another limit to accurate positioning of the fibers to PIC waveguides for large channel count.

Grinding of the grooves by CNC machine offers both high accuracy and flexibly in fiber placement in addition to the ability to create precision depth grooves as alignment features such as for dummy fibers or alignment pins or other elements. Another currently available innovation is lidless FAUs. When a lidless FAU is flipped upside down, the highly accurate fiber core center to cladding distance can be used for alignment to PIC waveguides. Another possibility, not yet commercially available but disclosed, is stacked fiber FAUs. [21] While it benefits from avoiding the cost of the V-groove (~\$1), automation of assembly and the associated costs and ability to achieve high yield is to be determined. More likely in the near-term is the adoption of 80 mm diameter fiber and fiber ribbon for an improvement in linear I/O density. This becomes increasingly valuable for the shoreline limitations of co-packaging due to package substrate size constraints (from reliability issues of chip-to-package and package-to-board electrical interconnects). Longer term and significantly more challenging is PM ribbon (or SMF/PM composite ribbon), needed if externally laser sources continue to be an option for co-packaging – the challenge being alignment of the PM fiber axes of all fibers in the ribbon. It is on the other side of the purple brick wall. (See the reference for a detailed analysis of internal vs. external lasers. [18]) Less challenging is fiber ribbon able to withstand solder reflow. Materials exist (like PMMA) but they are not easily applied. New ink formulations would also be required. Beyond this, multi-core fiber for even greater linear density (~30 mm pitch) could be needed for co-packaging with ever increasing channel count. Even further out could be the space-division technology of mode-division multiplexing shown in the 2045-time horizon. Of course, a more straight-forward but more energy intensity approach is coherent transceivers and QAM modulation format to greatly reduce I/O channel count.

With all the advantages as the incumbent technology, the disadvantages of FAUs are further cost reduction, increasing the scale of manufacturing and decreasing installation speed. Fiber loading, epoxying, dicing, polishing, and testing are currently labor-intensive, manual processes so the move to manufacturing in low-labor cost countries has already occurred. Equipment is already fully depreciated, and automation requires CAPEX that raises the equipment cost as it increases production volume. And installation speed is limited by FAU-to-PIC epoxy cure time and has the burden of its individual depreciation time on an expensive 6-axis tool.

An alternative to separate, actively aligned glass V-grooves are silicon V-grooves integrated in the PIC. They eliminate the need for expensive alignment equipment by enabling passive alignment with a pick & place tool (with additional care for the pigtails or fiber spools.) Also, silicon V-grooves within a silicon PIC have no thermal walk-off which is critical to quantum applications. Finally, they are easily scalable to high fiber counts and is a standard offering on a 300 mm wafer process platform but take up valuable silicon real estate, are hard to rework, still require adhesive curing, and currently have loss just under 2 dB, higher than the purple brick wall target. [22]

FAUs will continue to be a dependable PIC interconnect technology for a long time to come but newer approaches will take over as cost reduction and scale-up of 400G and faster transceivers drive the market. One such approach is laser bonding rather than epoxy to avoid lengthy cure times. [23] Another approach is novel use of a silicon interposer with dry-etched U-grooves for dummy guide fibers to passively align the PIC and FAU which are flip-chip assembled. [24] It is a passive alignment concept for potentially high-speed assembly that has not yet been demonstrated.

### **GLASS WAVEGUIDES**

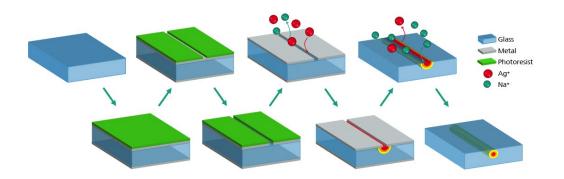

For integrated optic waveguide fabrication, several material platforms can be used including silicon, indium phosphide, silicon nitride, lithium niobate, polymer, silica, and glass. [25] These differ greatly in their advantages and disadvantages and therefore are selected depending on the application. If low cost, high dimensional stability and both passive electrical and optical interconnects are required, glass substrates and waveguides made by femtosecond-laser writing (fs) and ion-exchange are very well suited [26] for both wafer and panel formats. For fs-laser writing, the energy of a single photon is lower than the bandgap and the refractive index modification is achieved by multiphoton processing. [27] This method can write full 3D waveguides. It can also create alignment features self-aligned with the waveguides with a laser damage and etch process. However, it is a sequential process with throughput limitations. Ion-exchange in molten salts is a well-known process in the glass industry (e.g., smartphone cover glass) for batch chemical strengthening of glass by exchanging potassium for sodium ions. In 1972, Izawa and Nakagome were the first to use the increase in refractive index to fabricate waveguides using ion-exchange. [28] Since then, the process has been further developed resulting in many publications showing the high potential of this technique and demonstrating a wide range of components. [29] The silver ion-exchange waveguide fabrication on large panel sizes (457 mm x 303 mm) was demonstrated on display glass with low propagation loss of 0.06 dB/cm. [30] The process has the potential for up-scaling to larger formats. The ionexchange process parameters are dependent on glass diffusivity characteristics and need to be adapted to new glasses. The overall process flow for making glass waveguides by thermal ion-exchange are shown Figure 7: (a) glass panel, (b) thin film deposition, (c) resist dip-coating, (d) laser direct imaging and etching, (e) silver ionexchange, (f) mask removal, (g) reverse ion-exchange with sodium ions and (h) laser singulation.

Figure 7: Process steps for ion-exchange on glass starting with glass panels (step a) which have been metallized (step b) to provide a diffusion mask and lithographic patterned in step d. The ion-exchange is done in steps e and g [26].

### **IPSR-I DATACENTERS & TELECOM**

Because of the performance and reliability requirements, a glass with very low bulk absorption and waveguide longevity over the operating temperature is required for co-packaged optics. The waveguides are exposed to elevated temperatures over many years inside a package of a high-performance computing chip with significant heat dissipation of hundreds of watts. Of course, alkali-glass for ion-exchange from display applications could be considered but with trade-offs in waveguide longevity or optical loss performance. An optimized glass will be required with limited ion mobility at operation temperature range to avoid additional coupling and bend propagation losses due to change in waveguide characteristics by mode expansion over time. Improved glass compositions show promising results meeting the longevity requirements of 5 years at 110°C. [31]

For cutting glass waveguide circuits, high-speed laser singulation with optical-quality end-facets are required to achieve low-loss optical edge coupling to optical fibers. Laser cutting has significant advantages compared to other processes because they provide non-contact, near-zero kerf, no tool wear or the need for lubricants. [32] Laser singulation with controlled crack propagation by  $CO_2$  laser creates optical end-facets along straight lines. Alternative, laser-based methods utilizing quasi non-diffracting beams (e.g., Bessel beams) can be combined with ultrafast lasers [33] for partial end-face perforation in combination with application of mechanical force or thermal expansion (e.g., with a  $CO_2$  laser beam). The technique enables high accuracy, free-form cuts with reduced dependency on glass composition for cutting glass of all sizes. [34]