Photonic Systems Manufacturing Consortium

# 2015 ROADMAP DECEMBER 2015

A collaborative effort between the International Electronics Manufacturing Initiative (iNEMI) and the MIT Microphotonics Center.

Funded by the NIST Advanced Manufacturing Technology Consortia (AMTech) Program

# **PSMC TECHNOLOGY ROADMAPS**

December 2015

FOREWORD **ACKNOWLEDGMENTS** INTRODUCTION **EXECUTIVE SUMMARY** SITUATION ANALYSIS MARKET **TECHNOLOGY HIGHLIGHTED NEEDS PARADIGM SHIFTS** STRATEGIC CONCERNS **KEY RECOMMENDATIONS TECHNOLOGY ROADMAP CHAPTER HIGHLIGHTS EXPLANATION OF PRODUCT EMULATOR GROUPS TECHNOLOGY/MARKET DRIVERS PRODUCT EMULATOR GROUPS (PEGS) INTERNET OF THINGS PRODUCT SECTOR** DATA CENTER PRODUCT SECTOR **COST MODELING ENABLING TECHNOLOGY WORKING GROUPS (TWGS)** MONOLITHIC INTEGRATION TWG PACKAGING OF ELECTRONIC PHOTONIC SYSTEMS TWG INTERCONNECTION (CONNECTORS, CABLE ASSEMBLIES & PRINTED CIRCUITS)TWG **ASSEMBLY & TEST TWG APPENDICES** APPENDIX A: PSMC ROADMAPPING PROCESS APPENDIX B: ROADMAPPING PARTICIPANTS

© 2015 iNEMI

# Foreword

As we near completion of the first phase of our Photonic Systems Manufacturing Consortium's (PSMC) Five Year Sustainability Plan, we are releasing the first edition of the 2015 PSMC Integrated Photonic System Technology Roadmaps. This first PSMC Roadmap builds on the processes used and lessons learned from previous roadmap developments by the two PSMC Partners: The International Electronics Manufacturing Initiative and the MIT Microphotonics Center.

In spite of the fact that most companies and individuals are "oversubscribed" in their day jobs, approximately 400 professionals from more than 11 countries, representing than 160 more came together create organizations, to this product. Through sharing, analyzing, debating and reviewing, this diverse team contributed to these first roadmaps.

In July 2015 Vice President Biden announced that AIM Photonics was awarded the Integrated Photonics Institute for Manufacturing Innovation (IP-IMI). PSMC had committed in our Sustainability Plan and April 2015 Semi-Annual/Technical Progress Report to support the IP-IMI. The PSMC **PSMC Sustainability Mission Statement**: The PSMC will become a vital, industrysustained infrastructure element within the next five years. The PSMC value proposition is based on three pillars: Roadmap, "Big M" Technology Evaluation, and Supply Chain Integration. The pace of value creation is dependent on the emergence of cost effective, platformbased, high volume photonics manufacturing. Significant adoption of integrated photonics manufacturing is required during the next five years for PSMC to meet it sustainability goals.

Principal Investigators had communicated with the three contenders for the IP-IMI DOD Award. The PSMC Principal Investigators committed to play a major role in the Administration's Institutes for Manufacturing Innovation and subsequent entities under AMP (Advanced Manufacturing Partnership). 2.0 PSMC will cooperate and support all AMP entities in the development of a strong US integrated photonics manufacturing base. Professor Lionel Kimerling, PSMC Co-Principal Investigator has been appointed Executive of the AIM Photonics Academy, and Dr. Robert Pfahl PSMC Co-Principal Investigator, has been appointed Leader of the AMP Photonics Integrated Photonics Technology Roadmap.

The remaining task in Phase 1 of our Sustainability Plan is to develop a "PSMC Technical Plan." We will begin this process December 7, 2015 at the PSMC Workshop at MIT where participants will develop prioritized lists of gaps for each Technology Working Group. In the coming months these lists will be the foundation for AIM Photonics to develop a technical plan to help guide the selection of future R&D projects.

For our next roadmap we plan to add additional Technology Working Groups (TWGs) and Product Emulator Groups (PEGs) to address needs identified by AIM Photonics. We will begin this process with the formation of a Modeling, Simulation, and Design Tools TWG and a Sensors TWG in December.

We welcome your thoughts and comments as you use this important reference document in your planning processes.

Dr. Robert C. Pfahl, Jr.

Principal Investigator, PSMC Senior Consultant, iNEMI

Dr. Lionel C. Kimerling

Principal Investigator, PSMC

Thomas Lord Professor of Materials Science, MIT

# ACKNOWLEDGMENTS

## NIST AMTech

The preparation and publication of this roadmap was funded partially by a grant from the NIST AMTech program. Additional documents prepared under this grant include the *PSMC Sustainability Plan For the Integrated Photonics Integrated Manufacturing Institute*, published in January 2015

We extend special acknowledgment to those contributors who drafted, edited and summarized the materials in this document:

## **PSMC Executive Advisory Board (EAB)**

- Kal Shastri, Distinguished Engineer, Cisco

- Richard Otte, President, Promex Industries

- Terry Bowen, Fellow Corporate Technology, TE Connectivity

- Richard Grzybowski, Director of R&D, MACOM

- Bob Sankman , Intel Fellow, Intel

- Thomas Hausken, Senior Advisor, OIDA

- Katharine Schmidtke, Strategic Sourcing Manager, Facebook

- Lionel Kimerling, MIT, Ex Officio Member

- Robert Pfahl, iNEMI, Ex-Officio Member

## PSMC Leadership Committee

- Robert C. Pfahl, Jr, iNEMI, Principal Investigator, PSMC

- Chair, PSMC Data Center Product Emulator Group (PEG)

- Lionel C. Kimerling, MIT, Principal Investigator, PSMC

- Chair, PSMC Monolithic Integration Technology Working Group (TWG)

- Jim McElroy, iNEMI, Executive Director, PSMC

- Bill Bottoms, Third Millennium Test Solutions,

- Chair, PSMC Integrated Photonics Packaging TWG

- Richard Otte, Promex Industries, Integration TWG Chair

- John L. MacWilliams, Bishop Associates,

- o Chair, PSMC Interconnect (Connectors & Substrates) TWG

- Richard Grzybowski, MACOM,

- Chair, PSMC Internet of Things (IoT) Product Emulator Group (PEG)

- Randolph E. Kirchain, MIT, Emulator Cost Modelling Co-Chair

- Elsa A. Olivetti, MIT, Emulator Cost Modelling Co-Chair

## Technology Working Groups and Product Emulator Group Members.

The Technology Working Groups (TWGs) and Product Emulator Groups (PEGs) include a large number of industry, academic and government professionals. Members of each TWG are listed at the end of each Technology Roadmap. A complete list of roadmap participants can be found in *Appendix C*. More than 400 professionals from more than 11 countries, representing more than 166 organizations took the time to participate actively in the PSMC Roadmapping process either through the TWGs and PEGs or during three roadmapping workshops. Although we value the work of all participants and have made every effort to include them in these acknowledgments, probability dictates that a few organizations and/or individuals may have been left out. If that is the case, we apologize for any inadvertent oversight. Please note that the professional participants listed are respected as visionaries in their respective fields, and their views are not necessarily a reflection of the views of the entities where they work.

#### END USERS

Facebook Microsoft Intel

#### ORIGINAL EQUIPMENT MANUFACTURERS (OEM)

Alcatel Lucent Broadcom Ciena Cisco Systems Inc GE Global Research Harmonic Hewlett Packard Enterprise Huawei Technologies IBM Corporation Imaging Solutions Group Intel Corp. Juniper Networks LGS Innovations Nippon Telegraph and Telephone Corp.

#### **DEFENSE CONTRACTORS**

Boeing Lockheed Martin Raytheon Rockwell Collins United Technologies Corp

## ELECTRONIC/PHOTONIC MANUFACTURING SERVICES (EMS)

Celestica, Inc. Chiral Photonics Morton Photonics Photon Gear Promex Industries

#### ASSEMBLY EOUIPMENT MANUFACTURES

ficonTEC (USA) Corporation MRSI Systems New Scale Technologies, Inc. Palomar Technologies Tokyo Electron Universal Instruments

#### SEMICONDUCTOR EOUIPMENT MANUFACTURER SAMCO

#### TEST EOUIPMENT MANUFACTURER

3MTS, Inc. Advantest Corp. Keysight Technologies

#### TRANSEIVER SYSTEM/COMPONENT SUPPLIERS

Avago Luxtera Finisar Corp. NEL America Acacia Communications Inc.

#### **ROUTER AND SWITCH SUPPLIERS**

CoAdna Photonics, Inc. Compass EOS Mellanox Technologies

#### LASER & LED SUPPLIERS

Infineon LaserMax TeraDiode, Inc

#### ELECTRONIC PACKAGING SUPPLIERS

ASE U.S. Inc. Invensas Tessera

#### PHOTONIC SYSTEMS MANUFACTURER

Gooch and Housego

#### SUBSTRATE MANUFACTURERS

MFLEX TTM

#### CONNECTOR/CABLE MANUFACTURERS

Amphenol Intercon Systems Corning Inc FCI Molex OFS Samtec Ltd. Sumitomo Electric Industries, Ltd. TE Connectivity US Conec Ltd.

#### PRECISION OPTICS SUPPLIER

**Optimax Systems**

#### **MATERIAL SUPPLIERS**

3M Alpha Corning Inc. Dow Corning Dow Electronic Materials Henkel Corporation Heraeus SABIC

#### SEMICONDUCTOR MANUFACTURERS

Intel Corp. Analog Devices, Inc. Maxim Integrated Micron STMicroelectronics Texas Instruments Inc.

#### SEMICONDUCTOR FOUNDRIES

GLOBALFOUNDRIES IMT MOSIS

HETEROGENEOUS INTEGRATION OF InP MANUFACTURER Aurrion

#### SEMICONDUCTOR/PHOTONIC MANUFACTURERS MACOM

#### <u>FABLESS</u> <u>SEMICONDUCTOR/PHOTONIC</u> <u>MANUFACTURERS</u>

Qualcomm SiFotonics Technologies Sonas Systems Inc.

#### **DESIGN TOOLS**

Lumerical Solutions, Inc. Mentor Graphics MERL (Mitsubishi Electric Research Labs)

#### R&D CONSORTIA

AIST Ceramics Corridor Innovation Center CPMT iNEMI Institute for Defense Analyses ITRS MIT Microphotonics Center PETRA ReMAP SEMATECH

## <u>UNIVERSITIES/RESEARCH</u> INSTITUTES

Alfred University Ayar Labs Baker College Berkeley Wireless Research Center **Boston University** Columbia University Dartmouth College Draper Laboratory Fraunhofer HHI Fraunhofer IZM Ghent University IMEC LETI MATEC MIT MIT CSAIL MIT Deshpande Center MIT Lincoln Laboratory NICT/Waseda University Rochester Institute of Technology **Rutgers University** Singapore University of Technology and Design Southampton University Stanford University SUNY Polytechnic Institute SUNY Polytechnic Institute SUNY-CNSE Texas A&M University U. Delaware / MIT UC Berkeley **UC** Davis UC San Diego UC Santa Barbara **UMass Boston UMass Lowell** Università di Modena e Reggio Emilia University of Arizona University of Pittsburgh University of Rochester University of Southern California University of Tokyo

## **COMMUNITY COLLEGES**

OP-TEC QCC

## FEDERAL AGENCIES

Advanced Manufacturing Policy Office Air Force Office of Scientific Research NASA Goddard Space Flight Center National Science Foundation National Institute of Science and Technology Naval Research Laboratory OSD ManTech Support Sandia National Labs U.S. Army Research Laboratory

#### TRADE ASSOCIATIONS

ECIA IPC OIDA/OSA Semiconductor Industry Association (SIA)

#### PROFESSIONAL SOCIETIES SPIE

#### **CONSULTANTS/PUBLISHERS**

APEX Electrical Connector Consultants Bishop and Associates Inc ConnectorSupplier.Com Ghiasi Quantum LLC Information Gatekeepers, Inc. Saratoga Technology Sublimity LLC US Competitors LLC

## VENTURE CAPITAL/INVESTMENT

BANKERS Allied Minds Chromia Networks Jefferies LLC

# INTRODUCTION

On May 9, 2014 the National Institute of Standards and Technology (NIST) announced 19 advanced manufacturing technology grants awarded in the Advanced Manufacturing Technology Consortia (AMTech) Program. The Photonic Systems Manufacturing Consortium (PSMC), a consortium formed between the International Electronics Manufacturing Initiative (iNEMI) and the MIT MicroPhotonics Center - had anticipated the awarding of this grant and conducted its first Roadmapping Workshop in April 2014 to begin implementing the first of three phases of their proposal.

- Phase 1 Planning

- Phase 2 Execution of Plan

- Phase 3 Self-Sustaining Institute

PSMC received a grant of \$540,000 to execute the first phase of the program. During Phase 1 the PSMC is developing a strategic Roadmap and Technical Plan that i) identifies critical technical requirements for next-generation system integration and packaging, ii) details potential solutions to meet those requirements economically, and iii) identifies the technology supply chain limitations for commercial deployment of the required component performance in the 2015-2035 time frame. The Roadmap is responsible for i) promoting Design for Manufacturing (DfM) philosophy and ii) raising the issue of packaging science and engineering to significance for academic research and for allocation of industry and government resources. Three dedicated Workshops, two of which have been completed, are developing and cementing the Phase 2 goals.

The PSMC program addresses i) the unprecedented growth of data centers, ii) the increasing volume of internet traffic, and iii) the introduction of short reach optical interconnection in distributed architectures for communication, computing and sensing. The continued scaling of this massive growth and accompanying architecture changes requires the creation of a platform for the high-volume, low-cost manufacturing of integrated photonics. The nation that establishes the system design-for-function capability to address these needs, and the high volume, low cost infrastructure to manufacture high performance, energy efficient hardware will dominate the industry.

## PHASE 1: PLANNING

The PSMC strategy is centered on building a common manufacturing ecosystem that supports the Technology Supply Chain. The key outcomes of the Phase 1 planning stage are i) building mutual trust and cooperation among the supply chain stakeholders to establish a common vision for high volume photonic system manufacturing and for the technology gaps that need to be closed and ii) developing a cohesive roadmap for integrated photonic system design.

The PSMC Roadmap projects that a 1000 X increase in photonic system performance must be achieved at constant cost during the next decade. The advance of functional performance will require coordination of architecture, hardware, software and new application developments. Today's leading commercial firms may not be capable of surviving the reduction in margins as production volume is ramped higher. The PSMC is positioning its constituency to be the

complete Technology Supply Chain from materials-and-tools to end-users. The key to sustaining the Consortium Value Proposition is commercial application of the benefits of i) identifying roadblocks, ii) developing new technology and iii) practicing that new technology to build a common manufacturing learning curve. The PSMC strategic plan provides for ongoing Consortium-based development for the next 30 years.

The PSMC sustainability model for research, development, and manufacturing (RD&M) presumes development of a strong U.S.-centric supply chain that will draw industrial funding to the domestic research community to enable manufacturing growth. The PSMC Roadmap will continue, with the support of iNEMI and MIT Microphotonics Center, the specification of components, materials and technology needs at the system level.

The overarching goal of Phase 1: Planning is to create the processes and infrastructure necessary to conduct focused research and development during Phase 2. During Phase 1 we have integrated the roadmapping efforts of iNEMI and of the MIT Microphotonics Center to address the systems needs and the manufacturing needs of integrated photonics. We have organized the goals of the Phase 1: Planning into three "stages:"

- Stage 1: Initial Roadmap Development

- Stage 2: "Emulator" Development to Quantify needs

- Stage 3: Creation of the R&D "Technical Plan"

The Photonic System Manufacturing Consortium (PSMC) has facilitated a strong working relationship among the stakeholders to address both the research needs and the required manufacturing infrastructure for integrated photonics. To date more than 400 stakeholders from more than 160 organizations have participated in PSMC activities. This structure will serve the nation well in the Phase 2 execution phase of cooperative research and development to address the critical challenges for integrated photonics that are identified in the Roadmap.

The remaining task in Phase 1 of our Sustainability Plan is to develop a "PSMC Technical Plan." We will begin this process December 7, 2015 at the PSMC Workshop at MIT where participants will develop prioritized lists of gaps for each Technology Working Group. In the coming months these lists will be the foundation for AIM Photonics to develop a technical plan to help guide the selection of future R&D projects.

## PHASE 2- EXECUTION

In July 2015 Vice President Biden announced that AIM Photonics was awarded the IP-IMI (Integrated Photonics Institute for Manufacturing Innovation). PSMC had committed in both our Sustainability Plan and our April 2015 Semi-Annual/Technical Progress Report that we would support the IP-IMI. The PSMC Principal Investigators had communicated with the three contenders for the IP-IMI DOD Award. The PSMC Principal Investigators committed to play a major role in the Administration's Institutes for Manufacturing Innovation and subsequent entities under AMP (Advanced Manufacturing Partnership). 2.0 PSMC will cooperate and support all AMP entities in the development of a strong US integrated photonics manufacturing base. Professor Lionel Kimerling, PSMC Co-Principal Investigator has been appointed Executive of the AIM Photonics Academy, and Dr. Robert Pfahl PSMC Co-Principal

Investigator has been appointed Leader of the AMP Photonics Integrated Photonics Technology Roadmap.

In the Phase 2 of PSMC activities we will offer our experience in establishing an organization dedicated to manufacturing innovation; we will provide data and analyses based on our industry-wide strategic Technical Working Groups. The PSMC Technology Roadmap and supply chain coordination are critical elements for the AIM Photonics missions of manufacturing technology implementation and job creation. Definition of technology roadblocks and potential solutions will help structure AIM Photonics requirements; and technology timelines and cost analyses will help forecast the pace and content of the Education and Work Force Development in support of job creation. The PSMC technology targets, production and market data, and gap analyses will give continuous guidance to the IP-IMI strategic objectives.

## **PSMC WORKING GROUPS**

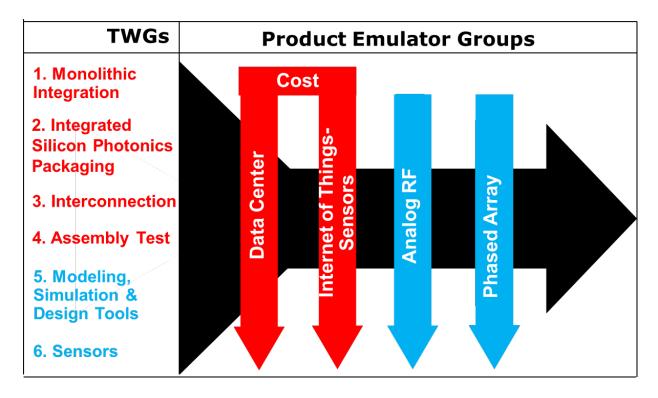

#### PSMC Technology Working Groups (TWGs)

During Phase 1 we have integrated the roadmapping efforts of iNEMI and the MIT Photonics Center to address both the systems needs and the manufacturing needs of integrated photonics. The four Photonic Systems Manufacturing Consortium (PSMC) Technology Working Groups (TWGs) have been established and are developing the roadmap. They are similar to existing iNEMI and Microphotonics Center TWGs, but they differ in scope. PSMC has been added to all TWG titles to mark this distinction in scope. The PSMC TWGs include many members from existing iNEMI-MIT groups, but their charters are more focused.

Since August 2014 the TWG leaders have been recruiting additional members and working with their TWGs. The four PSMC Technology Working Groups (TWGs) and their leaders are:

- PSMC Monolithic Integration TWG: Lionel Kimerling, MIT

- o Chips: silicon photonics, InP

- o Tradeoffs for cost, bandwidth density, power efficiency, and functional latency

- PSMC Packaging TWG: Bill Bottoms, Third Millennium Test Solutions:

- o Cost, materials, heat, footprint, port count, bandwidth, integration, functionality

- PSMC Interconnect (Connector & Substrate) TWG: John MacWilliams, Bishop & Associates

- Connectors includes: all separable interfaces within the system scope

- o PSMC Assembly and Test TWG: Dick Otte, Promex Industries

- Design for Manufacturing

- Assembly and Test

- Supply Chain Trade Offs

#### **PSMC Monolithic Integration TWG**

This PSMC TWG addresses chip-level integration on the Si and InP platforms; design for manufacturing; and tradeoffs for cost, bandwidth density, power efficiency, and functional

latency. The long term view will include identifying functional optical components such as optical switching. The chair of this TWG is Lionel Kimerling: <u>lckim@MIT.EDU</u>

#### **PSMC Packaging of Electronic Photonic Systems TWG**

This PSMC TWG focuses on the Packaging Technology and cost objectives needed to meet market requirements for low cost high volume photonic components and sub-systems for integration into the global network. Cost and performance objectives for system level, board level, package level and, where it is practical, chip level integration of photonics are the initial focus. Members will develop the needs for cost, materials, thermal, footprint, port count, and bandwidth. The chair of this PSMC TWG is: Bill Bottoms: bill\_bottoms@3mts.com

#### **PSMC Interconnection (Circuit boards, Backplanes and Connectors) TWG**

This PSMC TWG covers the intra-system connector and circuit board technology that will be needed for integrated photonic systems. Connectors include all separable interfaces within the system scope. Substrates include all circuit board and backplane components. The chair of this PSMC TWG is John MacWilliams: jmacwilliams@bishopinc.com

#### **PSMC Assembly and Test TWG**

This PSMC TWG addresses the development of manufacturing processes, materials and equipment to produce integrated photonic systems with ever decreasing cost and increasing volume. The PSMC TWG covers the needs for cost, integration, assembly, test, functionality, and tools. The chair of this PSMC TWG is Dick Otte: otte@promex-ind.com

#### **PSMC** Product Emulator Groups (PEGs) and Cost Modelling

In addition to the TWGs the PSMC working groups also includes Product Emulator Groups (PEGs) and an emulator group developing a cost model. The two Product Emulators have been defined utilizing input from the MIT Microphotonics Open Architecture System Optimization (OASO), the Leadership Committee, and the Executive Advisory Board (EAB). The emulators define the application needs and system performance targets, based upon an understanding of the consequences of parallelism, virtualization, and software defined networks.

#### **PSMC Data Center PEG**

Data centers are a critical node of network architecture that is driving higher bandwidth from the core network to ever shorter distances. As single channel data rates exceed 10Gb/s, copper transmission lines introduce excessive loss, necessitating a transition to photonic interconnects. The pervasive use of photonic interconnects at short distances means that photonic transport becomes a higher fraction of system data movement, requiring system design, architecture, software and hardware to be reconsidered. The Grand Challenges for information hardware are i) photonic integration for bandwidth density and ii) high volume manufacturing to meet the system demand. The chair of this activity is Bob Pfahl: bob.pfahl@inemi.org

#### **PSMC Internet of Things (IoT) PEG**

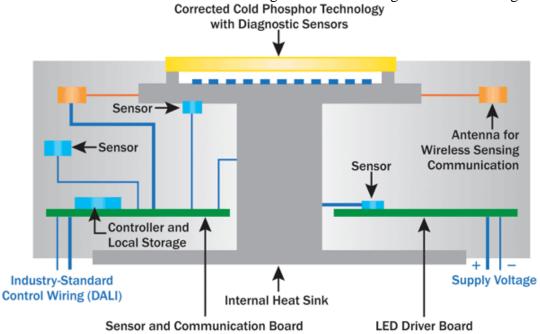

Chip-scale integrated photonic sensing systems are emerging as diagnostic sensors for medical, environmental and security applications; structural health monitoring; military sensing; and wireless sensor networks – the entire Internet of Things (IoT) space. The field is advancing rapidly, with fabrication technologies that leverage standard microfabrication infrastructure and enable the co-integration of sensors, photonics, electronics, and microfluidic sample preparation systems. The chair of this activity is Rich Grzybowski: <u>Rich.Grzybowski@macom.com</u>.

#### **PSMC Cost Model Development**

PSMC is developing technology-based models for the cost, energy, and environmental implications of various component and architecture alternatives for the two emulators under consideration. These process-based cost models (PBCM) will enable the modeling team to characterize how technologies will perform as photonics are integrated further into electronic systems. These tools also will serve to answer economic and energy use questions surrounding system architecture, enabling reliability and redundancy. Randolph Kirchain <u>kirchain@mit.edu</u> and Elsa Olivetti <u>elsao@mit.edu</u> are developing the PSMC cost emulator.

# **EXECUTIVE SUMMARY**

| SituationAnalysis                                                | 1  |

|------------------------------------------------------------------|----|

| Market                                                           | 1  |

| Technology                                                       | 1  |

| Highlighted Needs                                                | 2  |

| Standards Development                                            | 3  |

| Training of Designers                                            | 4  |

| Manufacturing Technologies                                       | 4  |

| Materials                                                        |    |

| Component Technology                                             | 5  |

| Security and Information Management                              | 5  |

| Paradigm Shifts                                                  | 5  |

| Strategic Concerns                                               | 6  |

| Key Recommendations                                              | 6  |

| Roadmapping                                                      | 6  |

| Design                                                           | 6  |

| Manufacturing Technology                                         | 7  |

| Materials Development                                            |    |

| Introduction to Chapter Highlights                               |    |

| Product Emulator Groups                                          |    |

| Data Center Product Sector                                       | 8  |

| Internet of Things Product Sector                                | 9  |

| Cost Emulator                                                    | 10 |

| Technology Working Groups                                        |    |

| Monolithic Integration                                           | 11 |

| Packaging of Electronic Photonic Systems                         | 12 |

| Interconnection (Connectors, Cable Assemblies, Printed Circuits) | 13 |

| Assembly & Test                                                  | 14 |

## **SITUATION ANALYSIS**

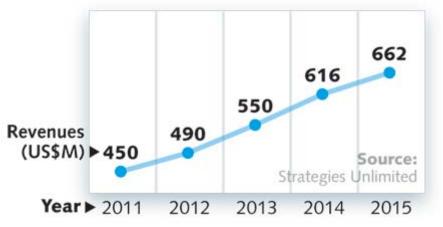

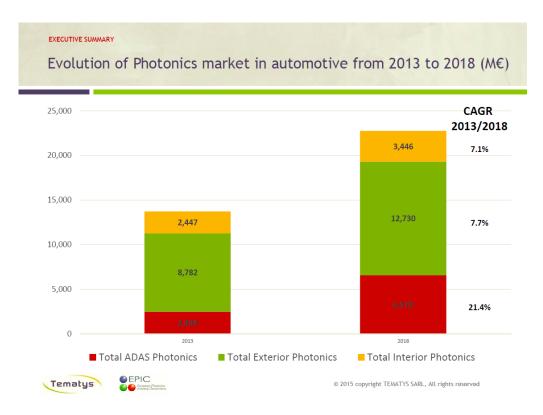

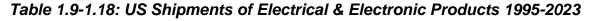

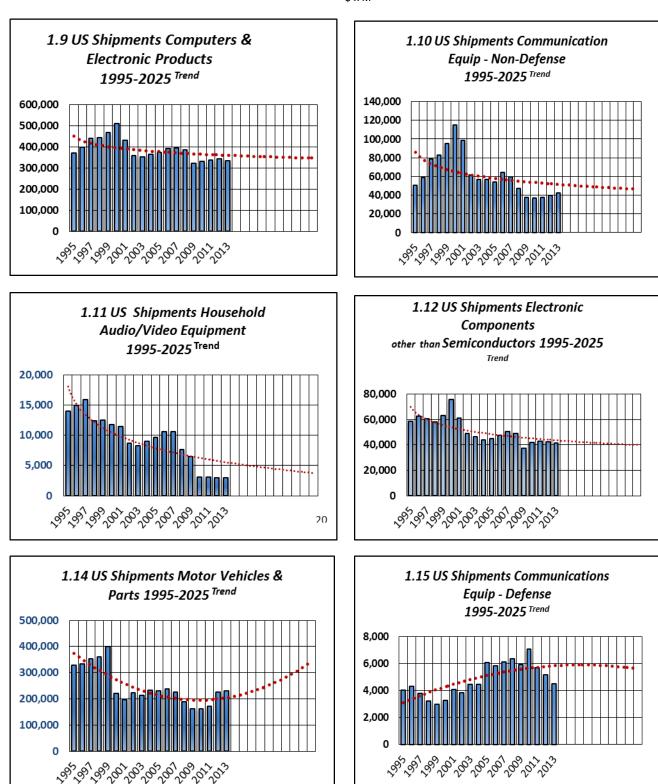

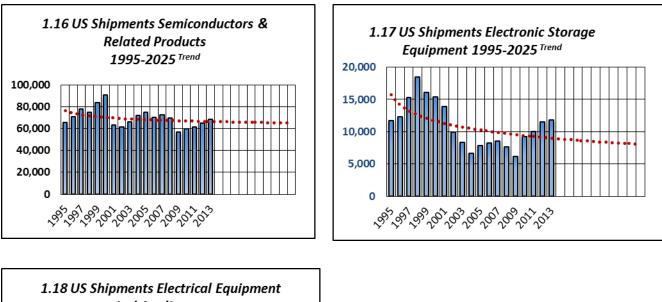

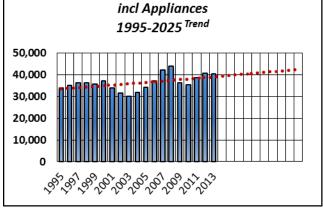

## MARKET

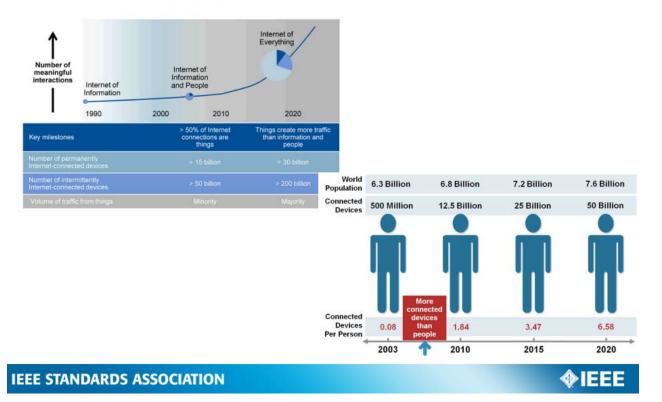

The boundaries among computers, communications and entertainment products have blurred. Flat panel displays are the norm for virtually all applications, with touch screen technology becoming dominant in a number of product categories. Wireless products continue to proliferate and this is opening up new applications in a number of segments. We are seeing dramatic growth of mobile Internet applications, including the massive demands for mobile data, the growth of mobile video, and the dramatic increase of smart phones as the gateway to the web.

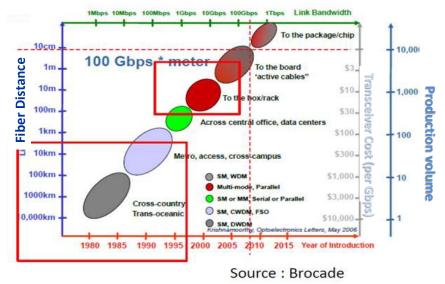

According to a June 2014 report from Cisco Systems, annual global IP traffic will surpass the zettabyte (1000 exabytes) threshold in 2016, and reach 1.1 zettabytes per year in 2016. Global IP traffic has increased more than five-fold in the past five years, and is expected to increase three-fold over the next five years. Overall, IP traffic is forecast to grow at a CAGR (Compound Annual Growth Rate) of 21% from 2013 to 2018.

End users desire more integrated, 'open-source' data center systems and the end users have emerged as a powerful factor in data center hardware selection. Consequently the center of power has shifted from OEMs to the large end users. The end users are establishing specifications for cost, energy, and bandwidth density. To reach their performance goals they are evaluating the impact of disaggregation, virtualization, direct memory access and microservers.

Today integrated optics technology is proprietary and not manufactured in high volume. Having multiple supply chain sources is difficult. Establishment of an enabling silicon photonics technology as envisioned in this roadmap is a necessary step to achieve low-cost, high-volume manufacturing in this rapidly expanding market.

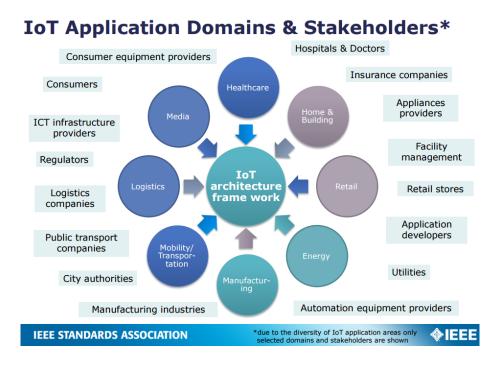

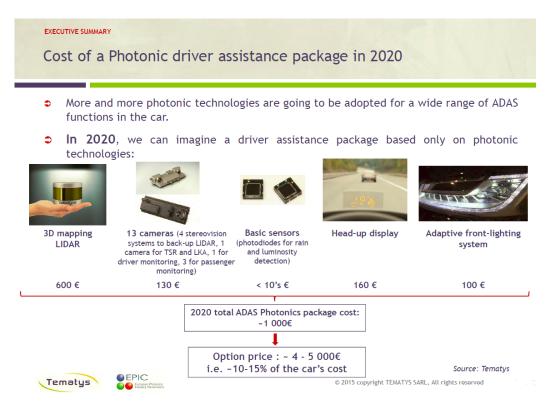

The Internet of Things (IoT) ecosystem is hard to define, complex, and difficult to capture due to the vast possibilities and the rapidity with which it is expanding. The available technology is being developed faster than new market opportunities can be identified. Key technologies for this market are improved low-power, high-speed communications and new sensors. These are technologies that integrated photonics systems are well positioned to address. The success of IoT depends strongly on standardization, that provides interoperability, compatibility, reliability, higher manufacturing volumes, and effective operations on a global scale.

## TECHNOLOGY

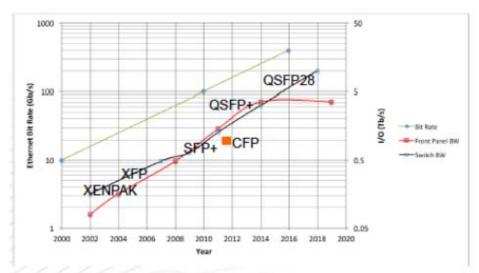

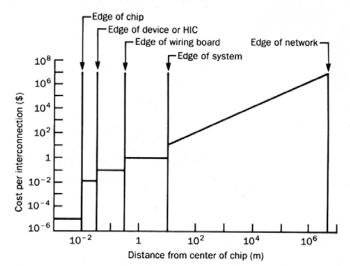

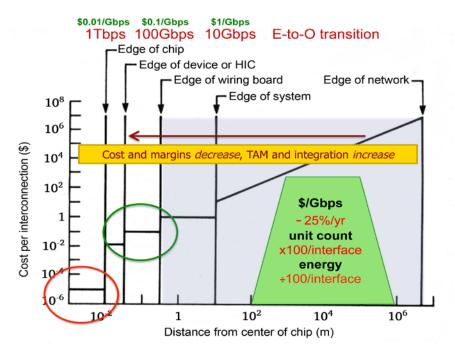

Cisco Systems projects that, globally in 2018, IP video traffic will be 79% of all consumer internet traffic, a five-year increase of 13%. This percentage does not include video exchanged through peer-to-peer (P2P) file sharing. The sum of all forms of video (TV, video on demand, Internet, and P2P) will be in the range of 80-90% of global consumer traffic by 2018. The telecommunications system and everything down to semiconductor chips must grow proportionally in both capacity and performance to support that traffic increase. In addition, new mobile applications require large amounts of computing power

resulting in warehouse computers that consume 50+ megawatts. These changes drive optical technologies. As these data rates increase, optical methods are replacing copper/electronic methods at ever shorter distances. The current transition point is at data rates of 10 Gb/s and distances of 1 to

10 meters. When data rates or distances greater than those are needed, optical methods are attractive because they often reduce both power consumption and physical size up to 75%.

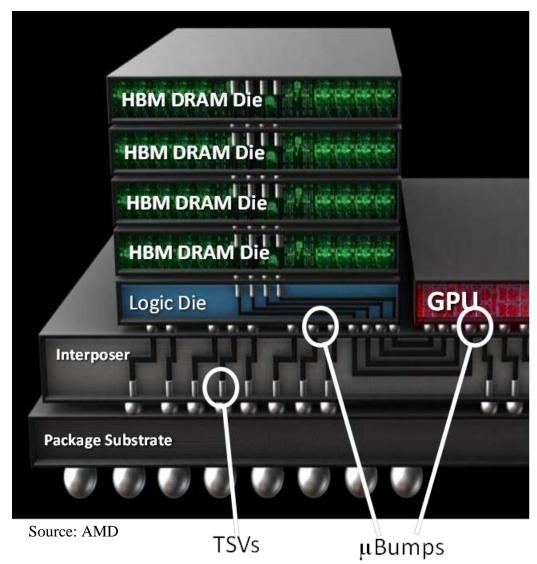

High-density 3D packaging of complete functional blocks has become the major technology challenge. By the end of 2019, CMOS process capabilities are forecast to be augmented by multiple new devices to implement functions beyond those of CMOS devices. However, since all of these new devices are unlikely to be compatible with CMOS processes, heterogeneous integration — either at the chip level or at the package level — will be needed to combine these new capabilities around a CMOS core. It is anticipated that this integration will be the most cost effective solution for silicon photonics.

- System-in-package (SiP) applications for portable products have become the technology driver for small components, packaging, assembly processes and high-density substrates.

- The demand for MEMS devices that provide higher performance, lower cost, new functions and integration of multiple sensor functions has led to the development of complex devices such as tri-axis accelerometers with gyroscopes and magnetometers, enabled new sensor device technologies, and advanced signal processing and communications interfaces.

- The interactions of light with matter are the basis for a variety of sensors that incorporate electronics for data processing and communications, either RF, electrical and optical.

- According to Yole Development, the first memories integrating 3D through silicon via (TSV) technology are in volume production, taking full benefit of MEMS processes.

## HIGHLIGHTED NEEDS

- During the 15 year life of this roadmap we must change the global network, the components in it and most of the elements attached to it, in order to meet the market needs of:

- 10<sup>4</sup> improvement in power efficiency

- 10<sup>4</sup> improvement in cost per function

- $10^6$  improvement in the number of network ports

All of these improvements are needed at no increase in total cost!

The potential sources of improvement are these:

- Disaggregation to improve the utilization of microprocessors from 15% to close to 100%. 5X

- 2. Microservers to replace blade servers. 10X

- 3. Direct memory access vs going through the internet protocols in data centers. 10X

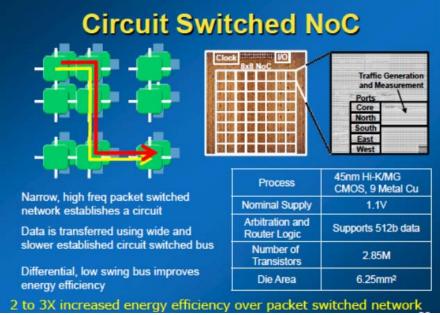

- 4. Broad implementation of circuit switching and switching in the optical domain. 10X

- 5. Further improvement in devices i.e. More Moore meaning CMOS at 10 nm nodes. 5X.

Optical methods that reduce power and increase data density will be widely used to implement these improvements.

More importantly, achieving this challenging task will require that the mechanisms for cooperation between industries and among researchers who are working in all advanced technologies must be strengthened. Cooperation among OEMs, ODMs, EMS providers and component suppliers is needed to focus on the right technology and to find a way to deploy it in a timely manner.

As noted in the introduction to this roadmap, the key activities of PSMC since May 2014 have been i) building mutual trust and cooperation among the supply chain stakeholders to establish a common vision for high volume photonic system manufacturing and for the technology gaps that need to be closed and., ii) developing a cohesive roadmap for integrated photonic system design.

The need for disruptive technologies to meet this challenge offer opportunity for innovation. In order to ensure success, the supply chain must be willing to invest with a long-term perspective in mind. The 2015 Roadmap has identified significant needs in a number of areas as highlighted in the following areas:

## STANDARDS DEVELOPMENT

The need for standards development has been identified in a number of areas of the roadmap. Many roadmap participants believe that the lack of timely standards is slowing significantly the implementation of technology and growth of markets. Several consortia such as the Consortium for On-Board Optics (COBO) are working to create industry standards that allow:

- Interoperability

- Interchangeability

- Broader market potential

With the need for standards acknowledged, note that standards generally emerge as the industry finds they offer value and adopts them. Standards are generally not imposed from some higher

## level. DESIGN TECHNOLOGIES

Design and simulation tools — or their lack of capabilities — can delay the rapid introduction of new materials and technologies. Particular areas where capabilities need to improve include:

- Modeling, Simulation, and Design tools for Integrated Photonic Systems;

- Design software able to utilize Hooke's General Law over temperature;

- Reliability, mechanical analysis and simulations;

- o Interfacial delamination,

- o Moisture modeling,

- Material characterization, and

- o Process modeling.

- Prediction of lifetime based on physics of failure;

- Thermal and thermo-fluid simulations;

- o Passive thermal management,

- Efficient and accurate thermal radiation, and

- Increased need for system level simulations.

## TRAINING OF DESIGNERS

Low cost, high-performance optical products start with good design. To effectively use this enabling technology requires that designers understand the technology and the manufacturing capabilities and limitations of the technology. Important factors that the designers need to understand include:

- Training of designers in Design for Manufacturing, Test and Cost;

- Minimizing the number of parts;

- Choosing parts that are adequate but not overly specified;

- Minimizing the number of assembly steps;

- Understanding details of parts and working with manufacturers to ensure that parts will have;

- The necessary dimensional consistency,

- o Suitable location reference points,

- Surfaces to which suitable joints can be made, and

- Shipping package containers that interface with manufacturing assembly equipment;

- Evaluating the extremes of part specifications and dimensional tolerances to ensure robust design;

- Maximizing the tolerances required as best as possible; and

- Ensuring that dimensional requirements can be achieved.

## **MANUFACTURING TECHNOLOGIES**

With research and development (R&D) responsibility shifting from OEMs to the ODMs and EMS companies, government, academia and industry consortia need to formulate new ways to adopt and develop emerging technologies into the manufacturing process. These new approaches will have to be consistent with viable business and funding required to create new industrial infrastructures. Specific manufacturing development targets include:

- Integrated photonics for high-volume applications,

- Process development to accelerate miniaturization,

- Assembly processes that support 3D structures and low-temperature processing,

- Cost-effective product traceability solutions,

- Anti-counterfeiting solutions,

- Reliability methodologies for manufacturing 3D structures, and

• Inspection/test technologies to keep up with increasing density of component packages.

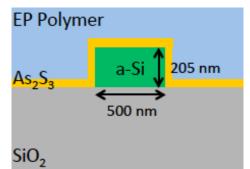

## MATERIALS

To meet the increased performance requirements of silicon integrated photonics will require the development of new materials with a variety of different properties. Insuring the reliability of these materials over the life of the product will be one of the gating issues for market introduction.

## **COMPONENT TECHNOLOGY**

A standard approach to package and board level interconnection is required to achieve low cost of key components such as:

- Printed wiring boards with embedded waveguides,

- Embedded waveguide-to-surface layer connectors,

- Surface mount interposers and sockets,

- Surface mount optical transceivers  $\geq$  100-400Gbps, and

- Direct Chip-Attach Optical Interconnect.

## SECURITY AND INFORMATION MANAGEMENT

Trusted foundries for military applications and component traceability, security, and anticounterfeiting protection for all applications are issues that must be addressed as new enabling technology is introduced.

## **P**ARADIGM **S**HIFTS

The predominant paradigm shift identified in this Roadmap is the impact of cloud-connected digital devices. The movement to the cloud has the potential to cause major disruptions across the electronics and photonics industries. In the next few years, the industry is likely to see major transitions in business models. We expect to see more of the following:

- Huge data centers operating more like utilities (selling data services),

- Local compute and storage growth may slow (as data moves to the cloud), and

- "Rent vs. buy" for software (monthly usage fee for cloud based solutions).

Other paradigm shifts identified in the 2015 PSMC Roadmap include:

- The need to continuously introduce complex multifunctional products to address converging markets favors the use of modular components or SiP (2D, 2.5D & 3D),

- The "Internet of Things" (IoT) is making sensors ubiquitous; however, there are concerns about network security as cyber-attacks become more pervasive, and

- The disruptive technology required to produce a 1,000 X improvement in data center performance at constant cost.

## STRATEGIC CONCERNS

- **Copper vs. Fiber:** Copper-based circuitry has advanced well beyond earlier capabilities and will continue to advance toward 100 GB throughput for short ~1m distances. There are companies working diligently on optical fiber solutions, but the number of companies doing this in the connector and PCB industries ≤ 10. There are a lot more making cable assemblies. At the core of optical fiber is one major US Company, Corning Glass.

- **Industry Cooperation**: Getting cooperation from industry personnel is difficult because of perceived IP issues involving their customers.

- **Cost Targets**: Proposed cost targets in an established industry are viewed as unrealistic unless standards are developed to commoditize the components.

## **KEY RECOMMENDATIONS**

## ROADMAPPING

For our next roadmap we plan to add additional Technology Working Groups (TWGs) and Product Emulator Groups (PEGs) to address needs identified by AIM Photonics. We will begin this process with the formation of a Modeling, Simulation, and Design Tools TWG and a Sensors TWG in December.

## DESIGN

The increasing End User and OEM focus on time-to-market and the complexity of emerging technology requires significant development and investment in design tool infrastructure. The following areas need increased research and development:

- Reliability, mechanical analysis and simulations;

- o Material characterization including optical properties,

- o Interfacial delamination and chip-package interaction (CPI),

- o Process modeling,

- o Environmental stress modeling,

- Moisture

- Temperature cycling

- Shock

- Etc.

- o Joint reliability modeling,

- Research and development of thermal and thermo-fluid simulations;

- Tools and methodology research and development in the manufacturing systems/supply chain management areas;

- Projected development and research for simulations in emerging areas (e.g., photonics, nano devices and materials);

- Co-design of optical, mechanical, thermal and electrical performance of the entire chip, package and associated heat removal structures; and

• New capability to close the gap between chip and substrate interconnect density.

## MANUFACTURING TECHNOLOGY

Manufacturing Technology has four strategic needs:

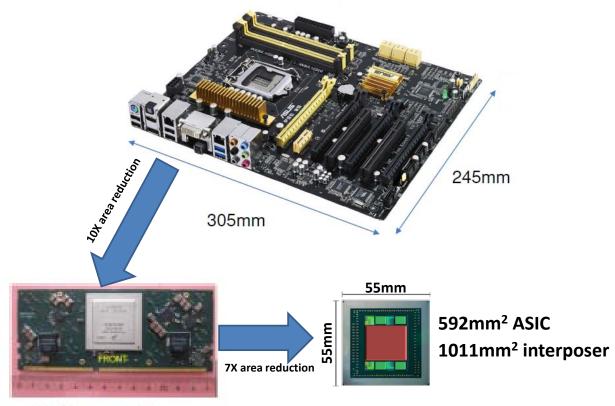

- 1. Miniaturization of the product,

- 2. Simplified, next-generation assembly processes,

- 3. Increased accuracy for assembling optical components, and

- 4. Fewer components to assemble.

These strategic needs generate the following recommendations in manufacturing technology:

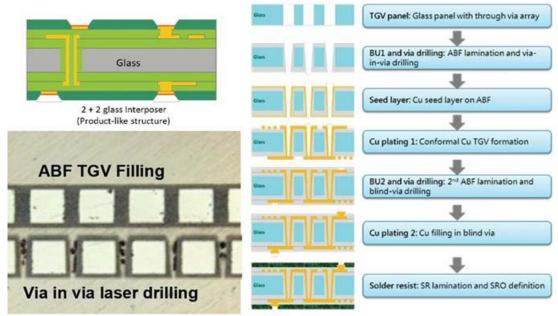

- New approaches to organic substrate manufacturing that provide dramatic increases in density, reduced process variability, electrical performance and significant cost reduction;

- Manufacturing processes at all packaging levels to deal with warpage and thin format products;

- 3D package stacking development with emphasis on;

- o Assembly,

- o Testing,

- Cooling, and

- o Reliability

- There are compelling advantages of 3D TSV technology; however, commercialization is gated by the development of the industry infrastructure and the supply chain;

- Low-temperature assembly, and

- Self-aligning assembly and stress free joining technology for photonic components.

## MATERIALS DEVELOPMENT

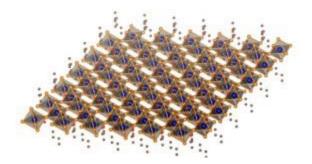

- A combination of materials and fabrication research is needed to support the development of monolithically integrated optics and electronics that take advantage of the electronics infrastructure.

- Low-cost, higher thermal conducting packaging materials, such as adhesives, thermal pastes and thermal spreaders.

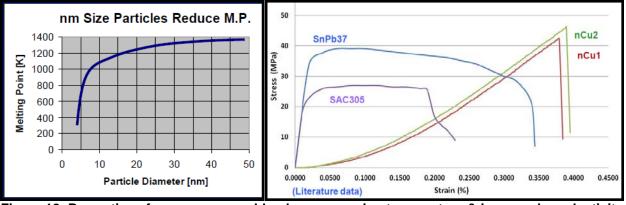

- New interconnect technologies deploying nano-materials to support decreased pitch and increased interconnect frequencies.

- High-performance laminates that are competitively priced.

- Clearer specifications for new materials, which are supported by a broad base of customers, to increase market size and reduce the risk for materials R&D.

- Reliability testing methodologies for new materials.

## **INTRODUCTION TO CHAPTER HIGHLIGHTS**

A list of key roadmap drivers was developed for each of two product sectors, known as PEGS. Key parameters for the Product Sectors will be tabulated in *Appendix A* after the Fall 2015 PSMC Workshop.

The Technical Working Groups (TWGs) use the projected technology needs from Product Emulators as input for the TWG Roadmaps. If the global electronics infrastructure can meet or exceed the key Product Sector drivers, through implementation of the strategies discussed in the 2015 TWG Roadmaps, then the industry can enable faster technology deployment and increased growth in global market for electronic products. The focus of PSMC's implementation activities is to identify gaps and issues that would prevent us from attaining these key parameters. PSMC will then support AIM Photonics in developing a five year technology plan which proposes projects to address prioritized gaps.

Because of the broad coverage of these roadmaps, many acronyms from diverse fields appear in the text. For reading convenience, an effort has been made to define an acronym the first time that it is used in a chapter.

## PRODUCT EMULATOR GROUPS

## DATA CENTER PRODUCT SECTOR

The Data Center Product Sector Emulator covers the technologies that enable high-performance computing systems, data centers, and communications systems. The data explosion generated by the growth in social networks and digital entertainment, cloud-computing, and IoT are radically driving the growth of data centers and the need for high bandwidth, low-latency communication.

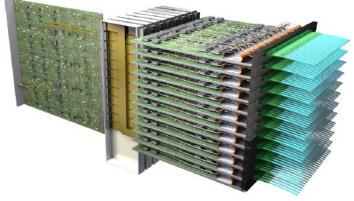

These forces are transforming the data center structures to a higher level of integration of computing, storage and networking components. The data bandwidth demand is resulting in systems with ever faster interconnect speeds, even as processor speed is staying constant. The size of the data centers creates a challenge for power demand creating an increasing focus on power efficiency of the systems. The data centers have an increasing number of systems residing in an environment of higher temperature, humidity and corrosive elements to reduce the operation costs and manage the total cost of ownership of these systems. Achieving this rapid growth places greater demands on increasing the performance and decreasing the cost of next generation equipment. Because of the capital requirements for adding capacity, all segments are undergoing rapid consolidation and movement to external cloud services.

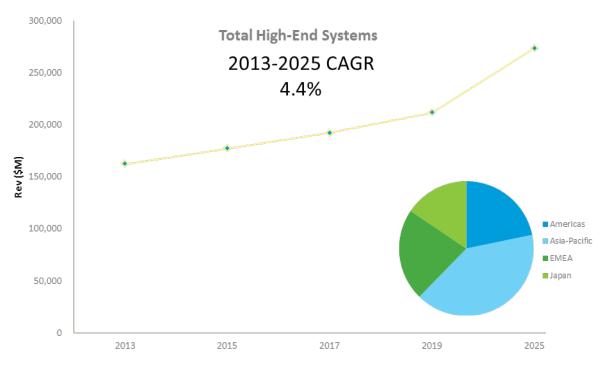

The industry analysis by IHS projects a factory OEM revenue growth of 4.4% CAGR over the next 10 years from a cumulative \$162B today to \$273B in 2025. The growth in the Data Center sector is particularly strong, growing from \$7B today to \$22B in 2025 driven by the rapid increase in data traffic. The rate of innovation in the Data Center sector is high, enabled in part by the open source concepts of hardware and software. The Enterprise Communications sector is still recovering from the economic meltdown of 2008-2009 and upgrades are slow. However metro networks are heavily utilized, with the proliferation of 4G and investments including 100G interconnect. The Service Provider Equipment is more closely tied to short term economic trends and forecast growth of 5.4% CAGR is driven by technology upgrades and convergence.

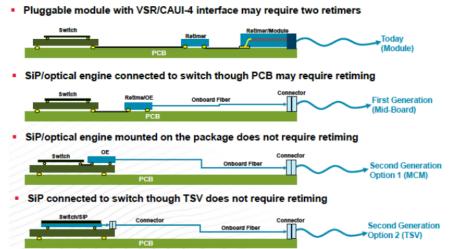

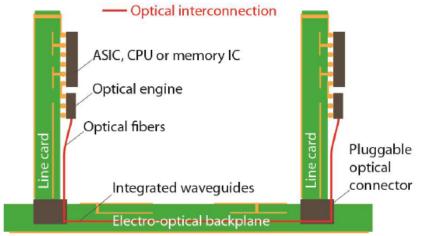

The assembly and packaging technology to support the data centers continues to advance. In particular the need for high-speed, low-latency data transfer is driving the need for integrated silicon photonic components. The enabling technologies include:

- Heterogeneous packaging (Through-Silicon Vias (TSV) for stacked chips and silicon interposers,

- System in Package (SiP) and Package on Package (PoP),

- integrated silicon photonics systems,

- lower loss interconnect (low-loss laminates in printed circuit boards and packages,

- More efficient power conversion (wide band-gap materials).

The Data Center Emulator focuses on enumerating the trends over the next decade that integrated electronics components and technology must meet for the Data Center Market. These trends particularly focus on:

- packaging technology and costs,

- PCB and connector technology and costs,

- Testing and assembly/joining technologies.

## INTERNET OF THINGS PRODUCT SECTOR

International initiatives like The International Year of Light (IYL) 2015, National Photonics Initiative (NPI), Horizon 2020, the BRAIN, and IP-IMI can only help reinforce what our industry already knows: Photonics plays a significant role in our daily lives and will only become more prevalent as future applications emerge!

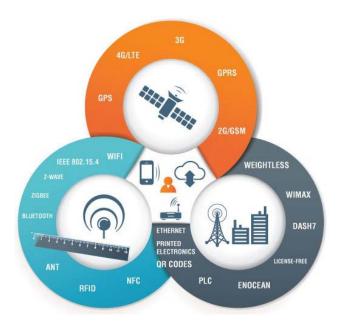

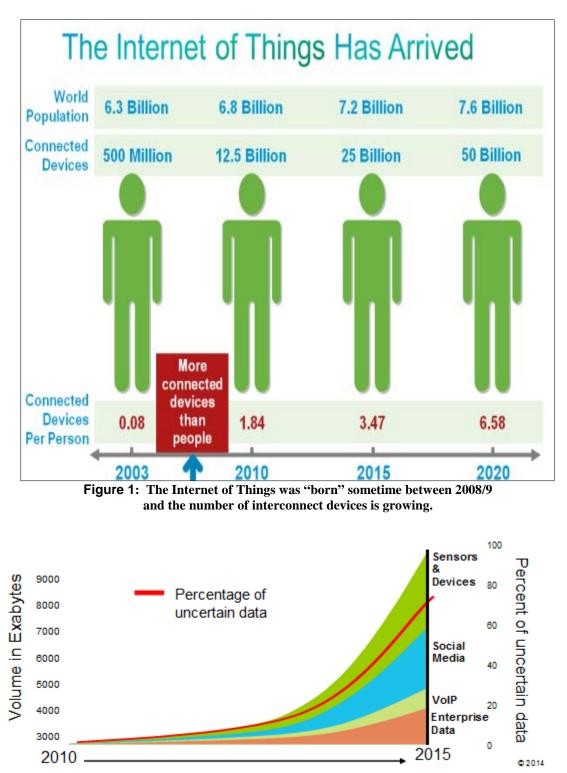

The impact of IoT on daily life is expected to be as great as the impact the internet has had in the last two decades. Thus, the IoT is recognized as "the next phase of internet". Enabling technologies include sensors and actuators, Photonics, Wireless Sensor Network (WSN), Intelligent and Interactive Packaging (I2Pack), real-time embedded system, Micro Electro-Mechanical Systems (MEMS), mobile internet access, cloud computing, Radio Frequency ID (RFID), Machine-to-Machine (M2M) communication, human machine interaction (HMI), middleware, Service Oriented Architecture (SOA), Enterprise Information System (EIS), data mining, etc. The IoT has, thus, become a new paradigm of the evolution of information and communication technology (ICT).

The IoT is expected to continually change and evolve – rapidly! More devices are being added every day and the industry is still in its infancy. Many of the challenges facing the industry are yet unknown. Given this, flexibility is needed in all facets of development. Processors and microcontrollers that range from 16–1500 MHz to address the full spectrum of applications from a microcontroller (MCU) in a small, energy-harvested wireless sensor node to high-performance, multi-core processors for IoT infrastructure. A wide variety of wired, wireless and photonic connectivity technologies are needed to meet the various needs of the market. A wide selection of sensors, mixed-signal and power-management technologies are required to provide the user interface to the IoT and energy-friendly designs.

The new technologies that are becoming available must meet these challenges – complexity, connectivity, security, bandwidth, power, and environmental. Key, new processor packaging technologies are being developed with some fundamental changes in the rest of the electronics

industry and how it impacts the technology that can be leveraged. With the IoT, a new set of technology will evolve, but often at a much different scale of size, bandwidth and latency than required by typical data centers.

## **COST EMULATOR**

The goal of the PSMC roadmapping effort is to identify the opportunities, obstacles and potential solutions to realizing broad adoption of photonics in a range of applications. In doing so, the industry will have the opportunity to coordinate resources and overcome those obstacles more efficiently. With a technology which is rapidly evolving, many potential solutions will be proposed to realize the future photonics vision. Each of those potential solutions will not only need to be vetted to ensure that they will provide adequate performance (e.g., speed and size), but also for their potential economic ramifications. It will be important to target industry resources on the portfolio of solutions which promise both the best technical and economic performance.

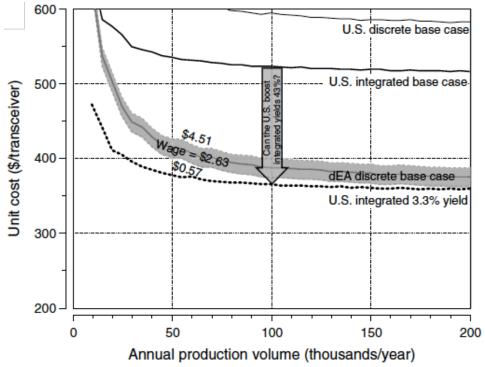

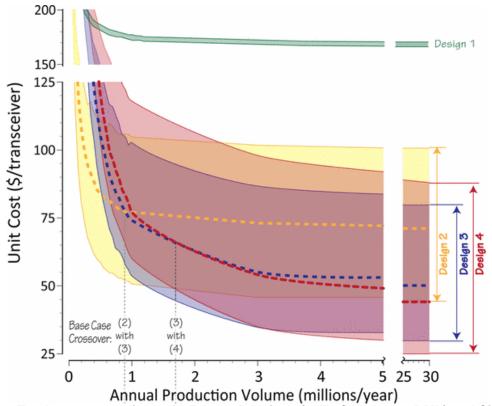

To address the latter part of this challenge, the PSMC roadmap is in the process of developing a generalized cost modeling tool that can be applied to bound the cost implications of proposed solutions. The goal of such a tool can be simply stated: to quantify the cost implications of proposed process flows. Such information should allow the roadmapping teams to focus their resources more rapidly – earlier in the technology development process. Currently, the PSMC cost modeling tool focuses on the costs of packaging and assembly. The goal is to eventually expand that scope to encompass all relevant production related costs. This chapter delves into the motivation for creating such a tool and then describes the current state of the PSMC tool primarily through a case example of optical transceivers.

We limit our analysis to only the packaging of the optical devices into a module. The costs of components are taken as inputs and are not calculated directly. Although we carry out sensitivities to understand the potential implication of various levels of component costs, the reader should view this analysis as incomplete. Although incomplete, this analysis serves to demonstrate the potential for details process-based cost analysis to critical photonics questions.

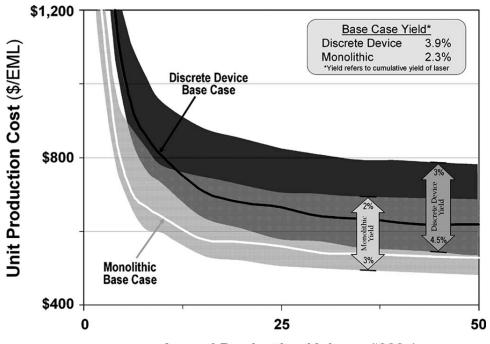

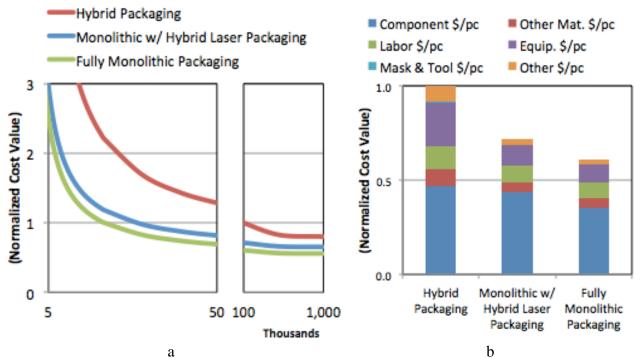

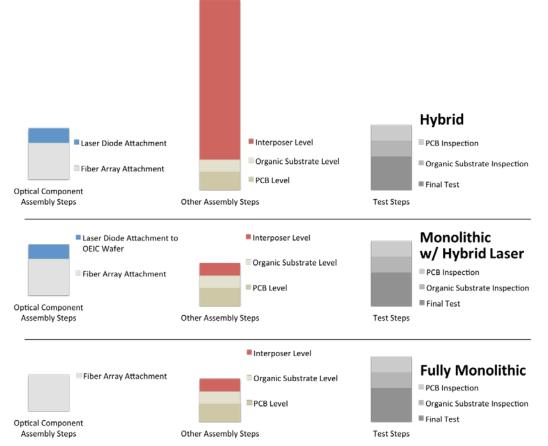

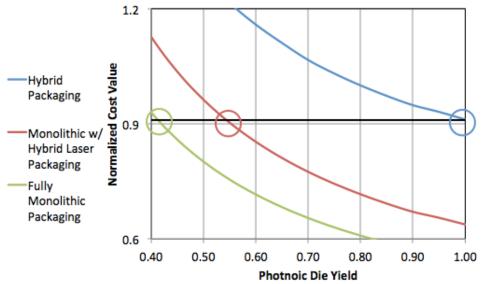

Preliminary results suggest that:

- Monolithic integration of the Datacom transceiver has the potential to significantly lower packaging cost for both high and low volume production;

- The key cost savings opportunity for integrating in the near term derives from avoiding the expense of assembling and packaging the interposer layer;

- Integration has significant cost advantages even if optical chip yields were to fall well below baseline modeled values.

## TECHNOLOGY WORKING GROUPS

Technology Working Groups (TWGs) in the 2015 Roadmap are:

- Monolithic Integration

- Integrated Silicon Photonics Packaging

- Interconnection

- Assembly & Test.

## **MONOLITHIC INTEGRATION**

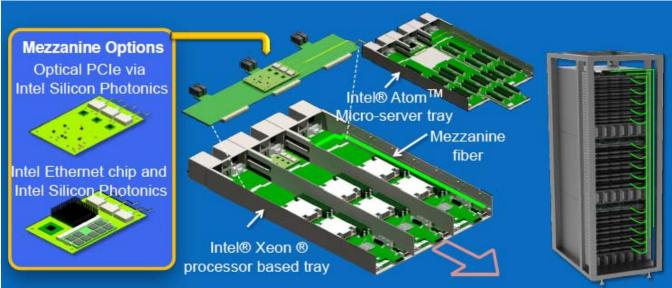

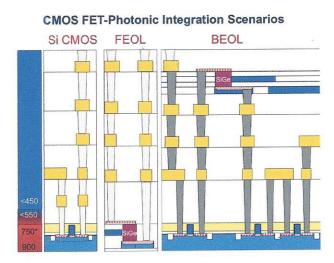

The PSMC Roadmap is a dynamic process, evident by the evolution of industry-wide semiconductor roadmaps over many years. The ITRS has reflected the semiconductor industry migration path from *geometrical scaling* to *equivalent scaling*. *Geometrical scaling* (e.g., Moore's Law) has guided targets for the previous 35 years, and will continue in many aspects of chip manufacture. *Equivalent scaling* targets improving performance through innovative system-level design, process, and software solutions that will increasingly guide the semiconductor industry in the future. Function-driven design requires incorporation of intelligent elements in the form of microprocessors, memory, and programmable logic devices built in silicon-based CMOS technologies. The *downscaling* of minimum dimensions enables the integration of an increasing number of transistors on a single chip, as described by Moore's Law. However, many quantitative requirements, such as power consumption and communication bandwidth no longer scale with Moore's Law.

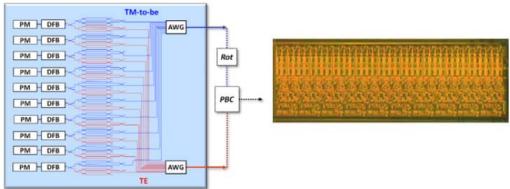

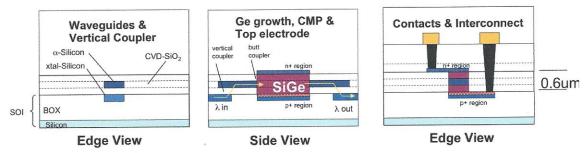

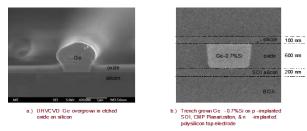

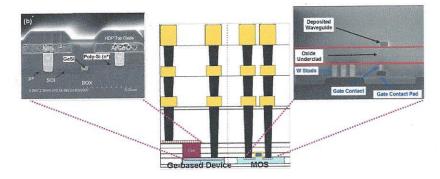

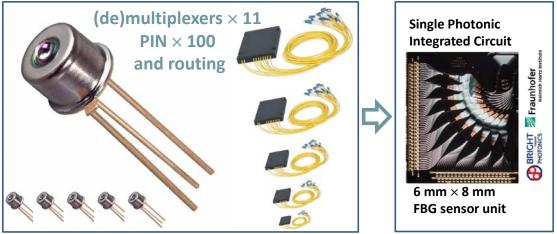

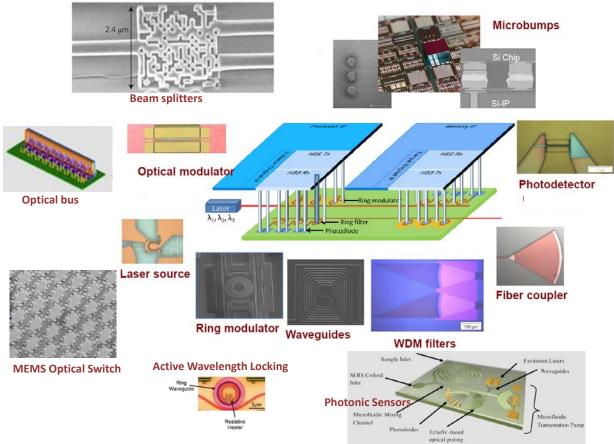

Integrated Silicon Photonics research, development and commercialization initiatives address new functionalities that do not necessarily scale according to "Moore's Law".

- SiPh packages containing Si detectors, GaAs and InP lasers in SiP or PoP multi-chip designs.

- Fully integrated ICs that may in the future contain CPU/ASIC and Si photonic transceivers.

The so-called More-than-Moore approach typically allows for these functionalities to migrate from board-level modular applications, such as discrete transceiver packages and board-level interconnects, into a package-level (SiP), chip-level (SoC), Stacked Chip SoC (SCS) or Package-on-Package (PoP) solutions. What will a fully integrated Si-Photonic subsystem look like; and what are its design objectives? Table 1 depicts a likely path for this technology transition: discrete devices, to hybrid package assemblies, to integrated die functionality, to integrated photonic system-on-chip. Table 2 shows the projected integrated silicon photonics component deployment timeline.

| Table 1. Silicon Photonics Technology Deployment |             |               |             |  |  |

|--------------------------------------------------|-------------|---------------|-------------|--|--|

| 2015-16                                          | 2017-20     | 2020-25       | Beyond      |  |  |

| Discrete                                         | Interposers | EO CPU/ASIC   | Logic-      |  |  |

| Devices                                          |             |               | Memory-IO   |  |  |

| EO                                               | InP VCSEL   | Si Lasers     | Integrated  |  |  |

| Transceivers                                     |             |               | SiPh SoC    |  |  |

| Interconnect                                     | EO          | Multi-Die SiP |             |  |  |

| Modules                                          | SiP/PoP     |               | Photonic    |  |  |

|                                                  |             |               | Systems     |  |  |

| MM                                               | Fly-Over    | EO/Waveguide  | Wafer-Panel |  |  |

| Connectors                                       | Cables      | PCB           | Substrates  |  |  |

| MM Cables                                        | MM-SM       | SM            | IO          |  |  |

|                                                  | Connectors  | Connectors    | Connectors  |  |  |

| AOCs                                             | MM-SM       | SM Cables     | Future WG   |  |  |

|                                                  | AOC         |               |             |  |  |

| Interconnects Packaging SiPh Integration         |             |               |             |  |  |

| Table 2. Silicon Photonics Components and Applications |                                              |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------|--|--|--|--|

| Technology                                             | Status                                       |  |  |  |  |

| 2015-16                                                |                                              |  |  |  |  |

| GaAs Lasers                                            | VCSEL arrays commercially deployed in        |  |  |  |  |

|                                                        | datacom                                      |  |  |  |  |

| InP Lasers                                             | Edge emitter arrays commercially deployed in |  |  |  |  |

|                                                        | telecom                                      |  |  |  |  |

| Ge-on-Si Lasers                                        | Research demonstration by several labs       |  |  |  |  |

| Ge-on-Si Detectors                                     | Fully waveguide integrated, commercially     |  |  |  |  |

|                                                        | deployed                                     |  |  |  |  |

| Waveguides                                             | Si, SiON, SiN commercially deployed          |  |  |  |  |

| SiP/SoC Assembly Technology                            | Electronics, but not photonics               |  |  |  |  |

| Si Photonic Integration                                | Commercially deployed in cable and board     |  |  |  |  |

|                                                        | assemblies                                   |  |  |  |  |

|                                                        | 2017-20 Projected                            |  |  |  |  |

| Ge-on-Si Lasers                                        | Early market entry                           |  |  |  |  |

| Ge-on-Si Detectors                                     | Pervasive commercial deployment              |  |  |  |  |

| Waveguides                                             | Pervasive commercial deployment, single      |  |  |  |  |

|                                                        | channel                                      |  |  |  |  |

| SiP/SoC Assembly Technology                            | Early 2.5 D deployment                       |  |  |  |  |

| Si Photonic Integration                                | Pervasive commercial deployment: cables      |  |  |  |  |

|                                                        | and boards                                   |  |  |  |  |

|                                                        | 2020-25                                      |  |  |  |  |

| Waveguides                                             | Pervasive commercial deployment: WDM         |  |  |  |  |

| SiP/SoC Assembly Technology                            | Pervasive commercial deployment: cables      |  |  |  |  |

|                                                        | and boards                                   |  |  |  |  |

| Si Photonic Integration                                | Emerging chip-to-chip intra-package          |  |  |  |  |

| Beyond                                                 |                                              |  |  |  |  |

| SoC Assembly Technology                                | Embedded in distributed circuit/system       |  |  |  |  |

|                                                        | architectures                                |  |  |  |  |

| Si Photonic Integration                                | Transceiver-less: embedded electronic-       |  |  |  |  |

| -                                                      | photonic synergy                             |  |  |  |  |

|                                                        |                                              |  |  |  |  |

#### **Table 2. Silicon Photonics Components and Applications**

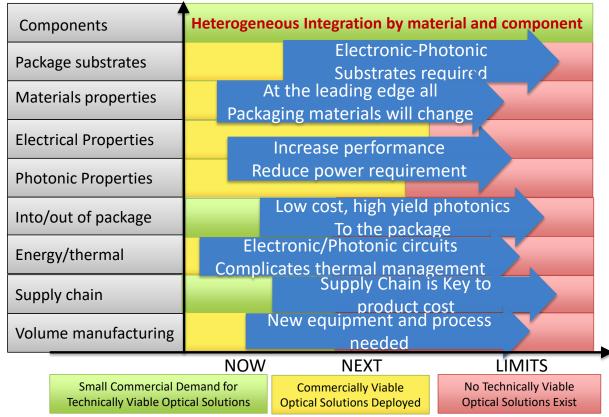

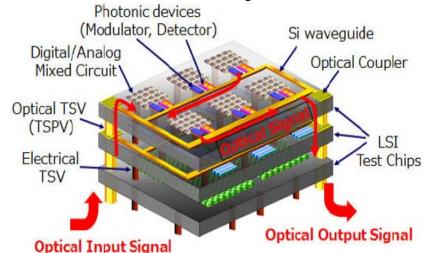

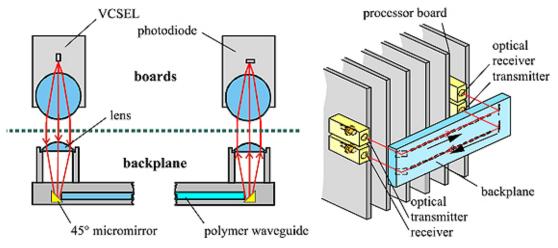

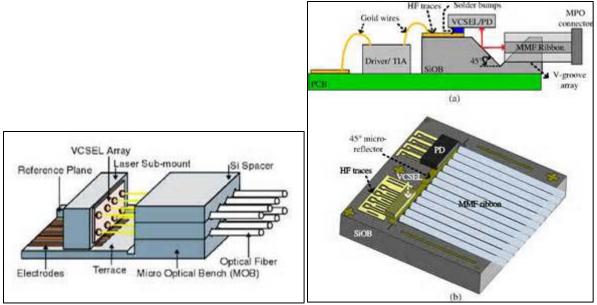

## PACKAGING OF ELECTRONIC PHOTONIC SYSTEMS

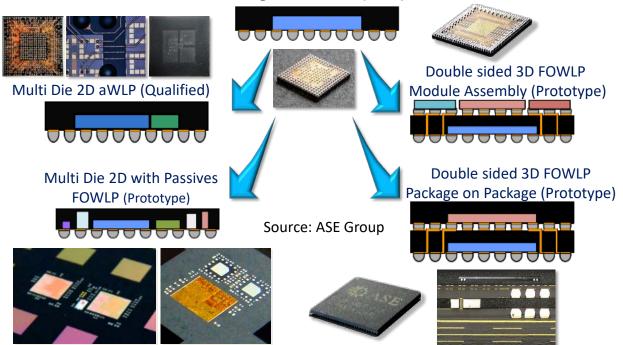

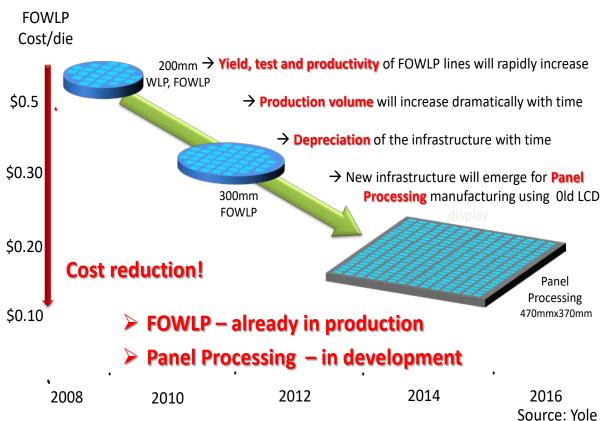

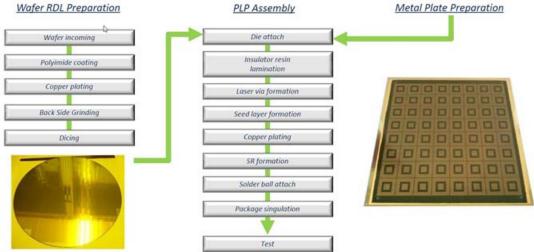

Packaging is a limiting factor in electronics today since it has not kept pace with Moore's Law in scaling. Today electronic packaging is more expensive than the package contents in many cases and it contributes substantially to increased power requirements and latency. The solution to these limiting factors is a work in process with innovations such as wafer level packaging (WLP), system in package (SiP) architecture, 3D integration and heterogeneous integration. The integration of photonics into these emerging electronic packaging solutions is a focus of this Chapter but continued innovation in other areas will be essential.

There will be many specific challenges in realizing the benefits of integrating photonics into the fabric of the global network and the components attached to it. The solutions, however, cannot come from just packaging photonic components. The co-packaging of electronics, photonics and plasmonics will be required to address these substantial new challenges to meet the expanding requirement for higher performance, higher reliability, increased security, lower latency and lower cost of the future.

There will be new device types, new materials, new package production processes and new equipment required to accomplish these objectives. Some of these required innovations we know today but many specifics that must be addressed over the next 15 years are not known. The objective of this roadmap chapter is to identify the challenges with sufficient lead time so they solutions can be identified and proven before they become roadblocks to the pace of progress for the industry.

The difficult challenges for the global data network over the next 15 years will be reducing the size, cost, power requirement and latency while delivering greater bandwidth and increasing reliability and security. The primary enabling factor will be the development of low cost, high performance photonic integrated circuits. These developments will address many of the manufacturing costs associated with the mechanical assembly of components on a printed circuit board and maintaining the mechanical stability required for photonic circuits. Packaging has been a limiting factor in meeting these requirements and it must be a major contributor in defining solutions for the future.

The essential functions that a package must be provided include:

- 1. Protection for the contents of the package from the use case environment

- 2. Delivery of power for operation of the package contents

- 3. Provide data paths meeting bandwidth and latency requirements of use case application(s)

- 4. Isolation of signals internally to avoid noise and cross talk

- 5. Thermal and stress management to meet requirements of the package contents

- 6. Do no harm such as adding to power requirements and latency due to the package

These essential functions must be provided with the smallest size and lowest cost possible. The focus of this Chapter is identification of the difficult challenges and the potential solutions for meeting these challenges well in advance so the challenges do not become "roadblocks" to continued progress. The primary integration technology for the potential solutions will be a complex, 3D System in Package (SiP) architecture.

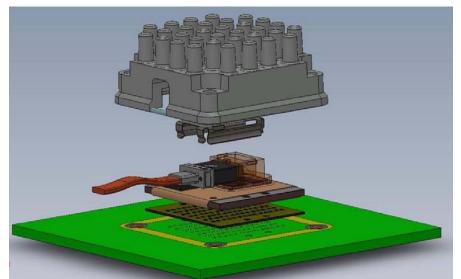

In order to identify the difficult challenges we are using two application areas from the Product Emulator Groups (PEGs) that will drive critical future requirements to focus our work.

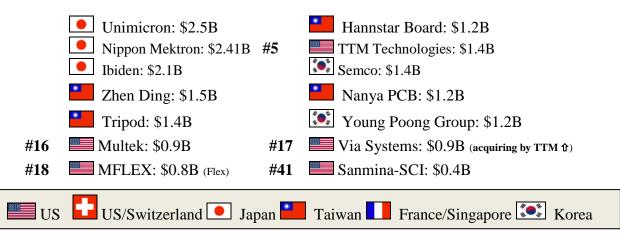

# INTERCONNECTION (CONNECTORS, CABLE ASSEMBLIES, PRINTED CIRCUITS)

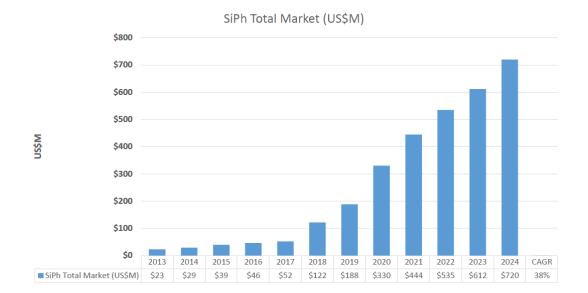

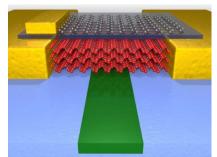

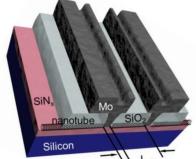

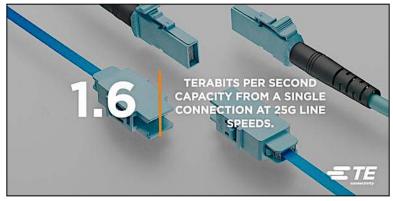

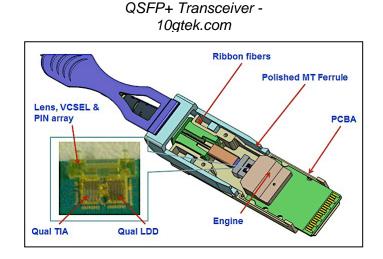

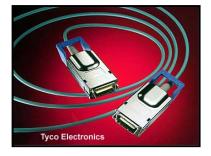

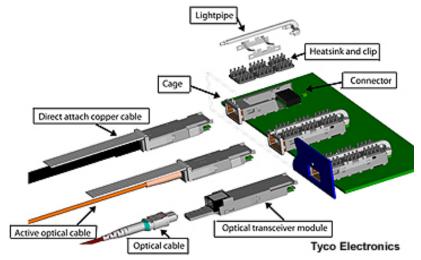

Silicon Photonics technology (SiPh) is defined as photonic (lightwave) circuitry that employs low cost Si as a device and circuit platform and employs heterogeneous micro-packaging of various photonic chips and devices including GaAs, InP, and preferably Si micro-laser technology to drive low cost/high volume Computer/Datacom/Networking/Video Streaming applications. The compelling requirement for these technologies will be increasing circuit speed and bandwidth. These requirements are surfacing in high performance computing, data communication networks and data centers. Terabit speed will be necessary by the 2020s. OEMs recognize this paradigm shift from Cu to photonic circuitry. OEMs such as Cisco Systems, IBM and Intel are working on these technologies at the chip and system level. Intel has announced its Omni Path Interconnect Architecture which will provide a migration path between Cu and Fiber  $\geq$  40Gbps.

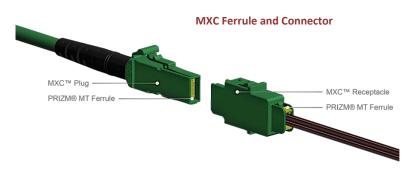

## The Interconnect TWG encompasses the following Technologies:

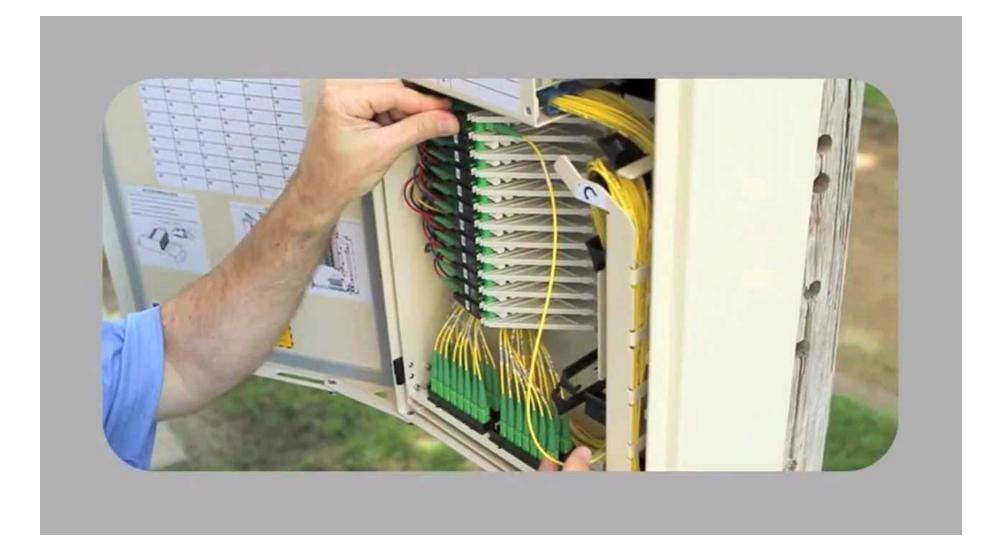

Existing and Fiber Optic Connectors (Focus on Single-Mode Fiber)

Future EO Sockets and/or Interposers (EO Conversion from Metallic IC Package) Existing and Future FO Cables and Transceivers (AOCs, Board-Level Transceivers) Printed Circuit Boards (Organic FR4 Derivatives with Embedded Waveguides or Fibers)

#### **Crosscutting Technologies covered in Packaging TWG:**

Interconnects within a SiPh SiP Package (Packaging TWG) Substrates employed in SiPh Multi-Chip IC Packaging (Packaging TWG) Direct Chip Attachment of SM FO Cables (SiPh Device TWG) Technologies Employed within the Semiconductor and IC Packaging Industries (Above)

#### Probable Future Technology Needs in Interconnect TWG:

- #1: Surface Mount Silicon Photonics for High Speed and Bandwidth (≥THz) Data Center, HPCC applications

- #2: Silicon Photonics MM Fiber in Internet2, IoT, Industrial, Medical and DOD applications for noise-immunity, environmentally rugged high speed and bandwidth applications (≤GHz)

#### **Probable Future Interconnect Product Designs (and Challenges):**

SM Fiber Optic Cable, PCB, IO Connectors (*Field Termination; Cost Targets*)

InP/Si RX/TX: Board-Level Modules, Active Cables (MM Designs in Production; SM Future)

Board Level Embedded Waveguide Connectors (No Existing; Technology/Assembly/Cost)

EOPCB with embedded waveguide and interconnect technologies

Chip to substrate or interposer electrical IO bump (copper pillar ?) densities down to <10 micron pitch from the ~50 micron in use today.

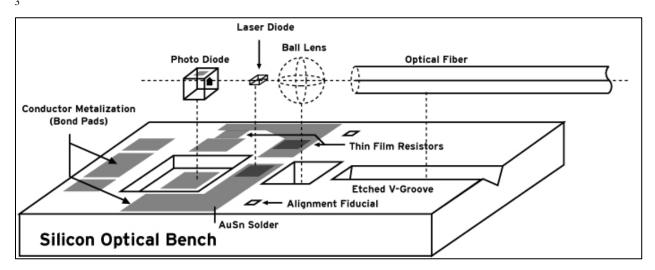

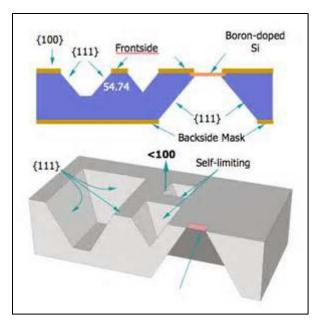

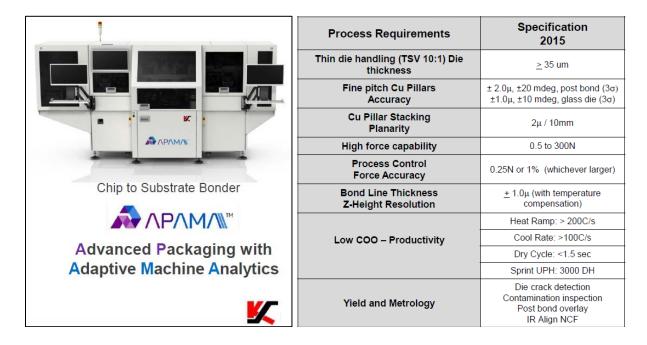

## ASSEMBLY & TEST

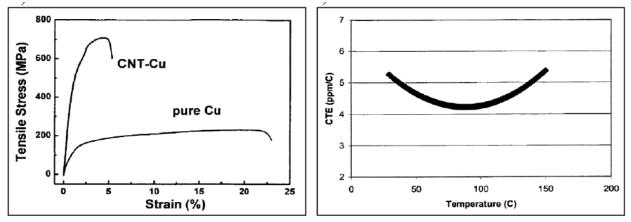

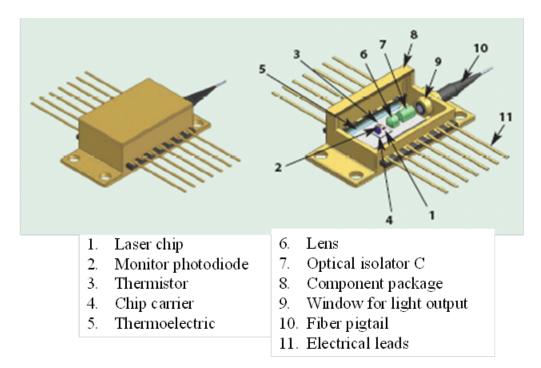

The overall cost, including especially the cost for assembly and test, of optical devices needs to be reduced substantially to make optical products cost effective in more applications. Many of the most important potential applications require single mode technology where assembly of parts requires tolerances and stability of the optical chains over the lifetime of the product in the operating environment of less than 1 micron. Achieving that level of mechanical consistency at low cost requires starting with the design, selecting materials and structures to minimize the effect of temperature and stress and other environmental phenomena, selecting materials, joining methods, and assembly processes that will yield that result.

Generally, materials with high modulus and low TCE are best and have been used extensively in optical devices. Unfortunately these materials tend to be expensive so much effort is devoted to utilizing lower cost materials and the lower cost processes. Detailed mechanical and optical properties of the materials used in optical products are often not available. Standardizing on those materials and making the properties available will enable designers to model optical products better and minimize the need to build and test hardware.

An obvious way to avoid assembly cost is to minimize the number of parts to be assembled. That is being addressed through the increased use of integration. Unfortunately, all of the functions needed in optical applications cannot be integrated yet so assembly, or heterogeneous integration as it is often called, is needed.

Assembly methods and equipment from the microelectronics industry are often the initial choices considered for optical products. Many of these processes are perfectly suitable for optical devices, especially the electronic and non-dimensionally critical functions. In addition, a sub set of the electronic methods are effective for the high stability design and assembly methods. The chapter emphasizes the character of joining methods and highlights those standard processes, materials and equipment that are suitable for that demanding requirement. Thermocompression bonding, welding and UV cured polymers are often good choices.

Processes to achieve the 0.1 micron tolerances required for true passive alignment of optical devices are not widely available. Many approaches are being investigated to fulfill that need and avoid expensive (because it is slow and requires expensive equipment) active alignment where the optical chain is activated and used to actually ensure alignment is adequate.

A common request is for "equipment able to align parts to <0.1 micron of accuracy." Equipment to achieve that level of accuracy is not yet readily available. What is available is equipment able to achieve 0.5 micron accuracy. That capability needs to be improved. To capitalize on the resulting equipment, other steps are needed; overall design, inclusion of fiducials and reference points, selection of stable joining methods and joining materials, etc. In addition, improved interfaces to equipment are needed. These interfaces must reduce programming, set-up and change over times to minimize the cost to build high mix low volume optical products.

Optical test is complicated by the need to provide not only optical sources and detectors but usually similar electronic functions as well. The 10 to 100 GHz speed of many optical devices requires expensive equipment. In addition, optical signals have many parameters that need to be both generated and measured; wavelength, power, modulation rate, modulation method, polarization, etc., often for many channels simultaneously. 12 channels are common today with roadmaps forecasting over 1024 channels in the future. Providing all those sources and detectors results in complex, expensive test sets.

# **PSMC INTERNET OF THINGS PRODUCT EMULATOR**

## Contents

| PSMC Internet of Things Product Emulator                | 1  |

|---------------------------------------------------------|----|

| Executive Summary                                       |    |

| Introduction                                            |    |

| Situation Analysis                                      | 3  |

| Roadmap of Quantified Key Attribute Needs (2015 – 2025) |    |

| Critical Infrastructure Issues                          |    |

| Technology Requirements and Trends                      |    |

| Conclusions                                             | 29 |

| References and Acknowledgements                         |    |

| Contributors                                            |    |

|                                                         |    |

## **PSMC** INTERNET OF THINGS PRODUCT EMULATOR

## **EXECUTIVE SUMMARY**

International initiatives like The International Year of Light (IYL) 2015, National Photonics Initiative (NPI), Horizon 2020, the BRAIN, and IP-IMI can only help reinforce what our industry already knows: Photonics plays a significant role in our daily lives and will only become more prevalent as future applications emerge!

The impact of IoT on daily life is expected to be as great as the impact the internet has had in the last two decades. Thus, the IoT is recognized as "the next phase of internet". Enabling technologies include sensors and actuators, Photonics, Wireless Sensor Network (WSN), Intelligent and Interactive Packaging (I2Pack), real-time embedded system, Micro Electro-Mechanical Systems (MEMS), mobile internet access, cloud computing, Radio Frequency ID (RFID), Machine-to-Machine (M2M) communication, human machine interaction (HMI), middleware, Service Oriented Architecture (SOA), Enterprise Information System (EIS), data mining, etc. The IoT has, thus, become a new paradigm of the evolution of information and communication technology (ICT).

The IoT is expected to continually change and evolve – rapidly! More devices are being added every day and the industry is still in its infancy. Many of the challenges facing the industry are yet unknown. Unknown devices. Unknown applications. Unknown use cases. Given this, there needs to be flexibility in all facets of development. Processors and microcontrollers that range from 16–1500 MHz to address the full spectrum of applications from a microcontroller (MCU) in a small, energy-harvested wireless sensor node to high-performance, multi-core processors for IoT infrastructure. A wide variety of wired, wireless and photonic connectivity technologies are needed to meet the various needs of the market. A wide selection of sensors, mixed-signal and power-management technologies are required to provide the user interface to the IoT and energy-friendly designs.

The new technologies that are becoming available must meet these challenges– complexity, connectivity, security, bandwidth, power, and environmental. Key, new processor packaging technologies are being developed with some fundamental changes in the rest of the electronics industry and how it impacts the technology that can be leveraged. With the IoT, a new set of technology will evolve, but often at a much different scale of size, bandwidth and latency than required by typical data centers.

## INTRODUCTION

The Internet of Things (IoT) is a key enabler for many emerging and future "smart" applications and technology shifts in various technology markets. They range from the Connected Consumer to Smart Home & Buildings, E-Health, Smart Grids, Next Generation Manufacturing and Smart Cities. It is therefore predicted to become one of the most significant drivers of growth in these markets.

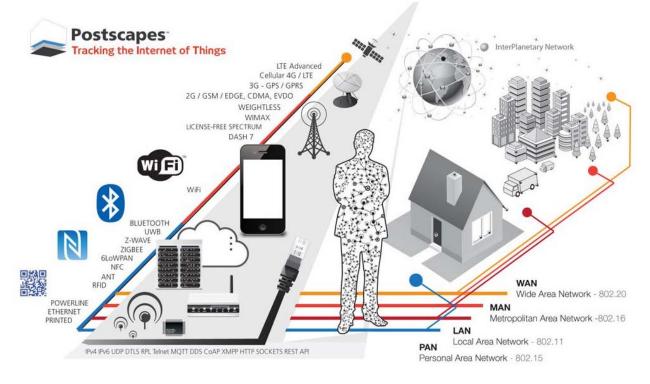

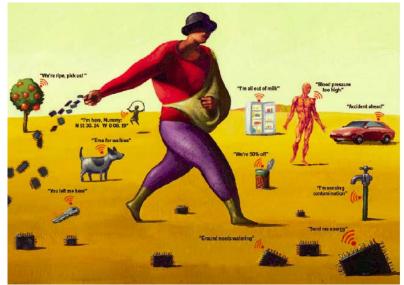

Broadly speaking, the Internet of Things (IoT) is a system consisting of networks of sensors, actuators, and smart objects whose purpose is to interconnect "all" things, including every day and industrial objects, in such a way as to make them intelligent, programmable, and more capable of interacting with humans and each other. The IoT is loosely defined as connections between devices, cities and people. It is, in essence, the seamless flow between the: BAN (body area network): the ambient hearing aide, the smart t-shirts; LAN (local area network): the smart meter as a home interface; WAN (wide area network): the bike, car, train, bus, drone, etc. and; VWAN (very wide area network): the 'wise' city as e-gov services everywhere no longer tied to physical locations. The IoT is actually a collection of vertical markets and industries — and references the way they will be affected by connected devices and consumers. In all - the IoT ecosystem is hard to define, complex, and difficult to capture due to the vastness of possibility and the rapidity with which it is expanding. There is no common definition of IoT, but it is shaping the evolution of the Internet, creating numerous challenges and opportunities for engineering and science and the success of IoT depends strongly on standardization, which provides interoperability, compatibility, reliability, and effective operations on a global scale.

IoT is the subject of a great deal of hype and many bold predictions about where it will eventually take us. However, there is no question that IoT is changing the world. In addition to connecting people, anytime and everywhere, it is connecting IoT products to humans and other IoT products, and it is putting these products at the service of humanity. This transformation has already begun; it will only continue to accelerate. Note that there can be many IoTs. There is the global IoT (evolving from the global Internet) as well as local and private IoTs. The term "IoT" encompasses all of these.

The Internet of Things (IoT) IEEE Ecosystem Study Executive Summary January 2015, IoT products include devices, apps, and services (e.g., smart phones, tablets, intelligent networks, big-data analytics, and cloud storage). A key aspect of IoT is the intelligent connectivity of these products. (It is likely that there will be situations where devices will be more rigidly constrained to satisfy safety, legal, and regulatory obligations.)"

## SITUATION ANALYSIS

## THE IOT MARKET AND PHOTONICS

**The IoT market** is burgeoning but fragmented. Early players are active and currently creating products for which they see a market. These players include government and academia as well as business and industry. In order to get products to market, these players are implementing proprietary solutions, some of which may evolve into de facto standards. Currently, IoT is trending toward vertical applications. Verticals showing early growth are consumer-goods, eHealth, transportation, energy and industrial automation. IoT development and deployment is motivated by the desire to provide existing goods and services more efficiently (cheaper, faster, better) and by the desire to create new goods and services that will drive new revenue streams. Connecting things and allowing data to move will open new markets, just as the Internet did. New products and business models will disrupt traditional business models; some of these new products and models will be created by unintended consequences of technologies being deployed.